Ultra-Efficient Nonvolatile Approximate Full-Adder with Spin-Hall-Assisted MTJ Cells for In-Memory Computing Applications

Abstract

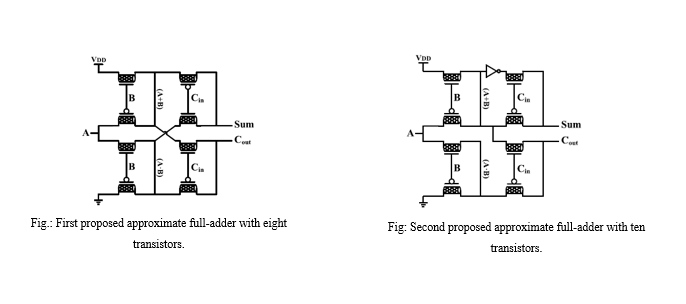

Approximate computing aims to reduce the power consumption and design complexity of digital systems with the cost of a tolerable error. In this project, two ultra-efficient magnetic approximate full adders are presented for computing-in-memory applications. The proposed ultra-efficient full adder blocks are coupled with a memory cell based on Magnetic Tunnel Junction (MTJ) to allow for non-volatility. Therefore, they can be power-gated when required. Both the proposed full adders have simple designs and are energy efficient. Instead of introducing dedicated write-driver and read circuits, the restorer latch inverters are utilized to contribute to the read and write operations, which results in a lower complexity. The peripheral circuitries are designed based on the Gate All-Around Carbon NanoTube Field-Effect Transistor (GAA-CNTFET).

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- H-spice

- Technology files: 45nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Introduction to approximate adders, Magnetic Tunnel Junction (MTJ)

- Need of ultra-efficient full adder blocks are coupled with a memory cell based on Magnetic Tunnel Junction (MTJ)

- Transistors & its applications

- Types of Transistors

- Logic Gates using Transistors

- Pull Up and Pull Down networks

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for approximate ultra-efficient full adder blocks are coupled with a memory cell based on Magnetic Tunnel Junction (MTJ)

- How to design low power, high speed area efficient transistor level circuits?

- Drawbacks in CMOS technology

- Scope of ultra-efficient full adder blocks are coupled with a memory cell based on Magnetic Tunnel Junction (MTJ) in today’s world

- Applications in real time

- H-Spice tool for design and simulation

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing