Performance Analysis of 4-Bit Multiplier using 90nm Technology

Also Available Domains Low Power VLSI|Tanner EDA

Objective

The main objective of this paper is to implement 4-bit multiplier to reduce the power consumption by using modified full adder.

Abstract

This research investigates the performance of three distinct 4-bit multipliers constructed using a modified full adder at the 90nm technology node. The study focuses on comparing the efficiency of low-power, high-speed multiplier designs against their CMOS counterparts. Given the substantial power consumption and impact on circuit speed associated with the multiplier module, the proposed multipliers aim to optimize and enhance overall circuit performance. Analyzing the results of our study, we observe that the proposed multipliers offer significant advantages over CMOS-based designs, including up to approximately power reduction, decrease in delay, and approximately decrease in transistor count, increase in speed by using 90nm technology

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

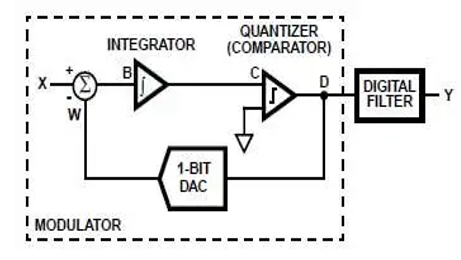

Block Diagram

Specifications

Software Requirements:

· Tanner tool

· Technology files: 90nm

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

Learning Outcomes:

- Introduction to Digital electronics

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Scope of multipliers in today’s world

- Applications in Real time.

- Tanner tool for design and simulation

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing