Parametric and Functional Degradation Analysis of Complete 14-nm FinFET SRAM

Also Available Domains Cadence EDA|Cadence EDA

Project Code :TVREBE19_17

Objective

The main objective of this paper is to analyze how aging impacts the parametric as well as the functional reliability of the memory

Abstract

Designers typically add design margins to compensate for chip aging. However, this leads to yield loss (in case of overestimation) or low reliability (in case of underestimation). This paper analyzes the impact of aging on a complete highperformance industrial 14-nm FinFET SRAM. It investigates the impact on the memory’s parametric (i.e., its delay) and functional (i.e., correct functionality) metrics. Moreover, it examines which components are the main contributors to the degradation of the memory’s reliability and how it is impacted by workload

and environmental conditions, i.e., temperature and voltage fluctuations. This paper not only investigates the impact of the memory’s components individually, which is typically the case in prior work, but it also studies the contribution of components’ interaction to the overall memory aging. The results show that

the timing circuit, address decoder, and the output latches and buffers are the main contributors to the memory’s parametric degradation, while the cell, sense amplifier, and address decoder are the main contributors to its functional degradation. Moreover, the results show that it is crucial to consider the impact of the interaction of components on the aging; individual analysis leads to overly pessimistic results and even wrong conclusions in certain cases.

and environmental conditions, i.e., temperature and voltage fluctuations. This paper not only investigates the impact of the memory’s components individually, which is typically the case in prior work, but it also studies the contribution of components’ interaction to the overall memory aging. The results show that

the timing circuit, address decoder, and the output latches and buffers are the main contributors to the memory’s parametric degradation, while the cell, sense amplifier, and address decoder are the main contributors to its functional degradation. Moreover, the results show that it is crucial to consider the impact of the interaction of components on the aging; individual analysis leads to overly pessimistic results and even wrong conclusions in certain cases.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

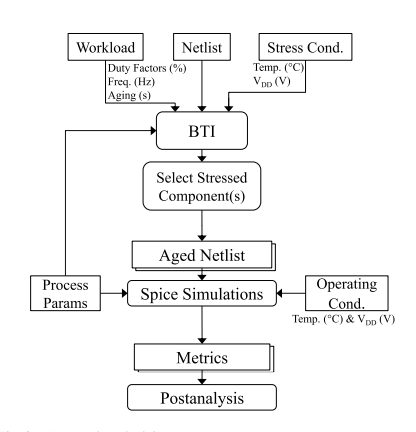

Block Diagram

Specifications

24/7 Support, Ticketing System, Voice Conference, Video On Demand, Remote Connectivity, Code Customization, Customization, Live Chat Support, Toll Free Support

Learning Outcomes

Basics of Analog and Digital Electronics

Related Topics

Paper Publishing

Paper Publishing