Low Error Efficient Approximate Adders for FPGAs

Also Available Domains Arithmetic Core|Xilinx Vivado

Project Code :TVMATO757

Objective

The main aim of this paper is to design low error efficient approximate adders for FPGAs. We are implementing the approximate adders based on optimized LUT based designs at the LSP of the adder implementation.

Abstract

In this project, we are aimed to design an

approximate adder which is based on LUT structures. In general whatever the implemented

approximate or accurate adders are mostly implemented in ASIC implementations

and sometimes based on the application when these modules are incorporated in

FPGA based applications which implies tat that the reprogrammable or reusable

circuits involves such ASIC based modules, these FPGA applications are unable

to meet the real time parameters as per the specifications. So in order to

apply it in Re programmable or re-usable circuits, here we are first

introducing two different 2 bit adders which are implemented using LUT

structures. After that these are utilized to construct n bit adder which is

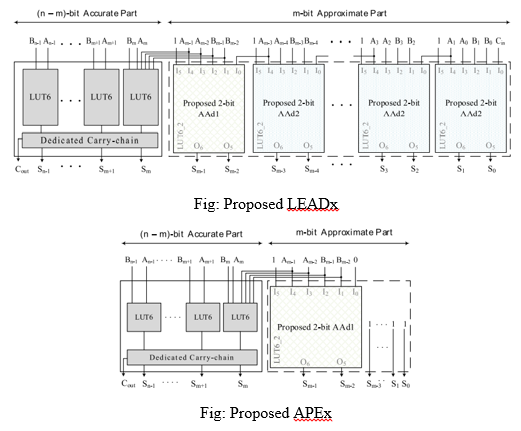

n-bit approximate adder. Based on the usage of the proposed two bit adders,

here we are suggesting two different n bit approximate adders. The two proposed

n bit approximate adders are LEADx (low error and area efficient approximate

adder) and APEx (area and power efficient approximate adder. Both approximate

adders are composed of an accurate and an approximate part. APEx has smaller

area and lower power consumption than the other approximate adders than the

existing adders. As a case study, the approximate adders are used in video

encoding application.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7 Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to Arithmetic circuits

- Knowledge on types of approximate adder circuits

- Different approximation techniques

- Knowledge on approximate FA adder designs

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Demo Video

Related Topics

Paper Publishing

Paper Publishing