Local Bit-Line SRAM Architecture With Data-Aware Power-Gating Write Assist

Objective

In this brief, a local bit-line (LBL) SRAM with data-aware power-gating write assist is proposed for near-threshold operation.

Abstract

This paper introduces a novel SRAM (Static Random-Access Memory) architecture that leverages data-aware power-gating write assist to enhance both energy efficiency and write performance. In an era of ever-increasing data-centric computing demands, the proposed architecture addresses the challenges of power consumption and write latency in on-chip memories.

The key innovation in this architecture lies in its ability to intelligently apply power-gating techniques to SRAM cells based on the data content being written. Traditional power gating typically involves completely isolating SRAM cells from the power supply during idle periods, incurring significant overhead when reactivating cells for write operations. In contrast, our data-aware approach selectively activates SRAM cells, reducing the overhead associated with write assist techniques.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

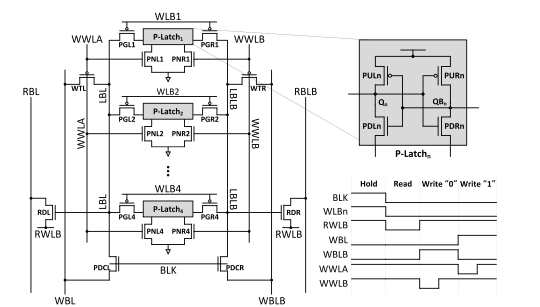

Block Diagram

Specifications

Software Requirements:

· Tool: Cadence Virtuoso

· Technology: GPDK45nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

· Introduction to digital & analog electronics

· Knowledge of MOSFETs

o Operation and characteristics of PMOS & NMOS

o Knowledge on Threshold voltages

· Basics of SRAM

o Operation of SRAM

o SNM and Power Analysis

o Stability Analysis

· Knowledge on Power Gating Concept

· Brief of Write assist techniques.

· Knowledge on Tool Learning

· Scope of SRAM in Real time.

Paper Publishing

Paper Publishing