Implementation of Smart Home using Finite State Machine Model

Objective

Security is always the need of the hour in a home. An automation system, which provides security as well as comfort, ensures reliability and ease.

Abstract

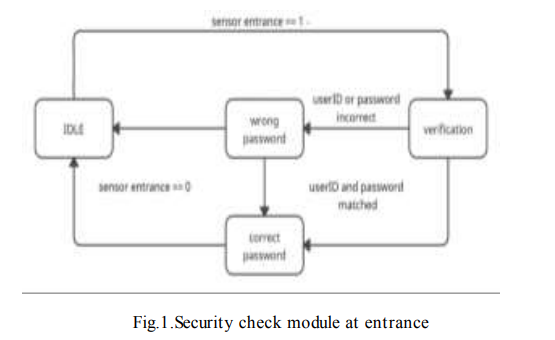

Security is always the need of the hour in a home. An automation system, which provides security as well as comfort, ensures reliability and ease. This helps making life convenient. A project with a system of detection of fire and intrusion through the doors and windows, which gives both comfort and security along with theft detection, fire alarm, heater, air conditione r, water tank and luminosity, gives not only a sense of security, but also comfort. A smart Verilog code for a smart home is implemented for the above features in this paper. A separate Finite State Machine (FSM) is used for each feature. Thus, synthesizing the Verilog code on Xilinx platform with verification of waveforms and simulation outputs are achieved.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software & Hardware Requirements:

Software used for this project is Xilinx ise for both synthesis and simulation purpose. One can use any synthesis tool like quartus prime, Xilinx vivado and many. Similarly one can use any simulation tool Xilinx vivado, model sim and many. One can use basys-3 for hardware purpose.

Paper Publishing

Paper Publishing