Fixed-Posit: A Floating-Point Representation for Error-Resilient Applications

Also Available Domains Cadence EDA|Arithmetic Core|Xilinx Vivado

Abstract

Abstract:

IEEE-754 floating point is the standard used today to represent real numbers in practically all computer systems. Recently, posit—which offers superior accuracy and a wider dynamic range—was suggested as a substitute for IEEE-754 floating point. Posit may be customized to have a different amount of regime and exponent bits, which has prevented widespread use. We suggest a fixed-posit format to address this flaw and show the construction of a fixed-posit multiplier. In this representation, the number of regime and exponent bits are fixed. Using the AxBench, OpenBLAS, and neural network benchmarks as well as error-tolerant applications, we assess the fixed-posit multiplier. When compared to posit multipliers, the proposed fixed-posit multiplier saves 47%, 38.5%, 22%, and up to 70%, 66%, 26% of the power, area, and latency of the 32-bit IEEE-754 multiplier, respectively. For workloads using OpenBLAS and AxBench, these savings come with a negligible output quality reduction (1.2% average relative error). Additionally, we see a tiny accuracy reduction (0.12%) when using the fixed-posit multiplier for neural networks like ResNet-18 on ImageNet.

Keywords: IEEE-754 floating point, Posit, Multipliers, Intel Pin, Power and Error analysis

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

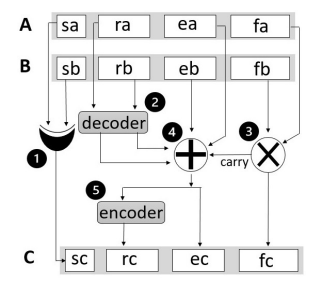

Block Diagram

Specifications

Specifications:

Software Requirements:

· Xilinx Vivado

Hardware Requirements:

· Microsoft® Windows 7

· Intel® i3 processor or equivalent with SSE support

· 4GB RAM

· 100 MB of available disk space

Learning Outcomes

Learning Outcomes:

- Introduction to VLSI

- Basics of Digital circuits

- Limitations & Applications.

- Introduction to adders

- Knowledge on different types of multipliers

- Applications

- Introduction to posit multiplier

- Working of posit multiplier

- Applications

- Importance of Verilog

- Xilinx Vivado tool for design and simulation

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation skills

Paper Publishing

Paper Publishing