Fast Binary Counters and Compressors Generated by Sorting Network

Also Available Domains Arithmetic Core|Xilinx Vivado

Project Code :TVMATO739

Objective

The main objective of this paper is to implement fast saturated binary counters based on sorting network to improve the efficiency of designs involving summation of multiple operands.

Abstract

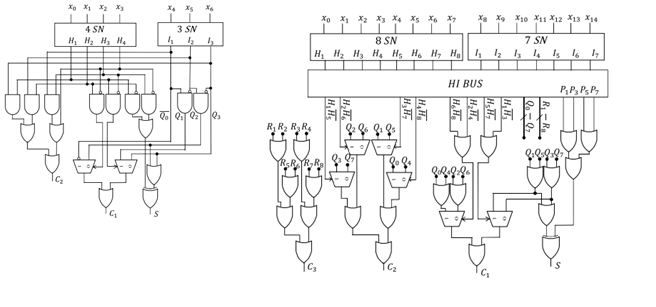

In this project, a novel method of fast

saturated binary counters such as (7, 3), (15, 4), (31,5) and exact & approximate

(4:2) compressors based on the sorting network. The inputs of the counters are first

divided asymmetrically into two parts and fed them as inputs to the sorting

networks to generate the reordered sequences, which can be solely represented

by one-hot code sequences. By using this method, we construct and further

optimize the (7, 3) counter that can perform better in maximum than other designs

in delay, area– delay product, and power–delay product, respectively.

Similarly, the (15, 4) counter is constructed, and it achieves shorter delay,

while it significantly consumes less power and area. Besides, we also construct

approximate (4:2) compressors based on sorting network. To analyze the

performance of the circuits designed, they are embedded in 8 x 8 using Full

adder, half adder & (7,3) counter, and for 16 × 16 bit multiplier using Full

adder, half adder & (7,3) counter, (15,4) counter.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7 Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to counters

- About sorting networks

- Knowledge on multiplier circuits

- Different higher ratio compressors

- Knowledge on multiplier designs using compressors

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Demo Video

Related Topics

Paper Publishing

Paper Publishing