Design of Approximate Multiplier less DCT with CSD Encoding for Image Processing

Also Available Domains Arithmetic Core|Xilinx Vivado

Abstract

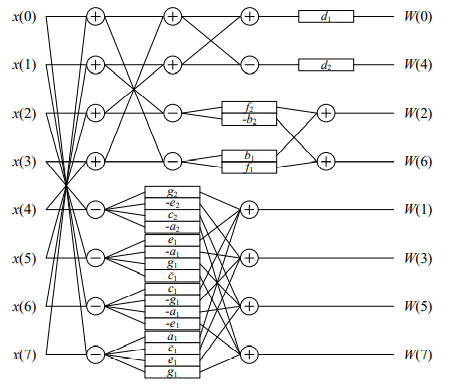

In this project, a multiplierless discrete cosine transforms (DCT) design with approximate canonical signed digit (CSD) encoding for image processing is proposed. Two approximation strategies on CSD encoding are proposed in constant multiplication. Based on these two coding approaches, an approximate DCT architecture is presented by taking advantage of the correlation between adjacent pixels of image data. Higher frequency coefficients are gradually ignored from the calculation due to the energy compaction property. Four approximate DCT architectures are thus proposed representing different accuracy levels. The proposed DCTs are implemented using 0.18μm standard CMOS process. The simulation results indicate that the proposed ADCT reduces power and area with a PSNR penalty of 1.6dB when compared with the traditional design. For lossy applications which allow lower computational accuracy, ADCT-III achieves reduction on the power consumption and area, at a cost of 11.7 dB accuracy loss. The effectiveness of the proposed method is synthesized and simulated using Xilinx ISE 14.7.

Keywords:- Approximate DCT, CSD encoding, multiplierless, pixel correlation, image processing

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP,

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to DCT

- Knowledge on CSD encoding

- Different multipliers

- Knowledge on shift and add operations

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing