An Efficient Way of Implementing High Speed 4-Bit Advanced Multipliers in FPGA

Objective

In this paper, two 4 bit multipliers purposed namely Unsigned Array Multiplier and Wallace Tree Multiplier.

Abstract

ALU in Digital processor is the important block as all the computational operations carried out by this. A multiplier is an electronic circuit used in any computing device for multiplication of two binary numbers. Multiplication of 4-bit numbers is a lengthy procedure if we go the conventional way. In this paper, two 4 bit multipliers purposed namely Unsigned Array Multiplier and Wallace Tree Multiplier. The Wallace tree method is highly pipelined and saves a lot of time. Individual components of both the devices are optimized and have been used to construct the multipliers. The designed circuit is implemented in FPGA (BASYS-3 ARTIX-7). The delay obtained in Wallace multiplier is lesses than the delay compared to previous literature

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

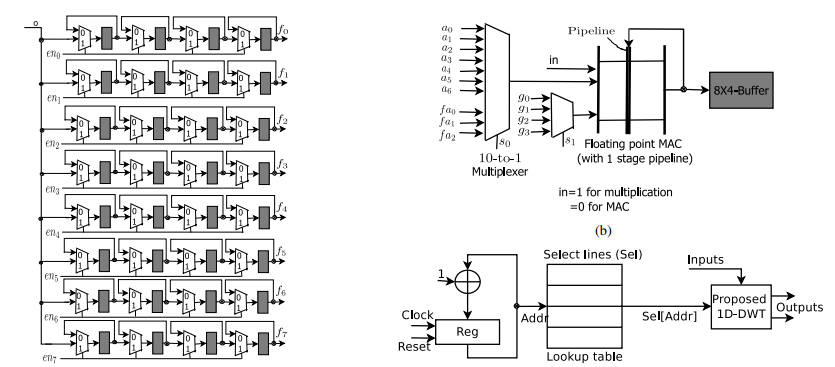

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing