A New Energy-Efficient and High Throughput Two-Phase Multi-Bit per Cycle Ring Oscillator-Based True Random Number Generator

Also Available Domains Transistor Logic|Low Power VLSI|Tanner EDA

Project Code :TVMATO711

Objective

The main objective of this work is to achieve the high throughput of Random number generation and make the system to be energy efficient. The proposed circuit is designed in a standard 45 nm 1.2 V CMOS process to perform the True random number generation.

Abstract

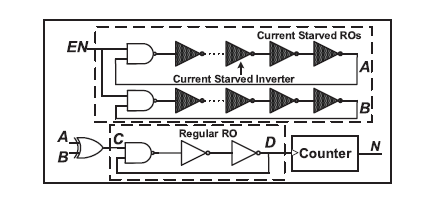

In this project, new lightweight TRNG

design is proposed to minimize

the power wasted by the superfluous oscillations. Random bits are

extracted from both phases of the slow ROs to increase the throughput and the

fast RO is activated only during the narrow transition time difference between

two symmetrically designed slow ROs. The slow jittery ROs are implemented using

current starved inverters biased in the weak inversion region to reduce their

power consumption. Their jitter amplitudes are increased by lowering the oscillation

frequency and reducing the drain current of the transistors. The narrow jittery

pulse generated by the differential pair of slow ROs is quantized by the

fastest three-stage RO. Two random bits from each phase of the jittery ROs can

be extracted by using a gigahertz dynamic toggled D flip-flop counter to count

the number of oscillatory cycles of the fast RO

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

Cadence Virtuoso

Technology files:180nm

Hardware Requirements:

Microsoft® Windows XP

Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

512 MB RAM

100 MB of available disk space

Learning Outcomes

- Introduction to TRNGS

- Need of TRNGS in Cryptographic applications

- Transistors & its applications

- Types of Transistors

- Logic Gates using Transistors

- Pull Up and Pull Down networks

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for TRNGS

- How to design low power, high speed area efficient transistor level circuits?

- Drawbacks in CMOS technology

- Scope of TRNGS in today’s world

- Applications in real time

- Cadence Virtuoso tool for design and simulation

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation skills

- Thesis Writing Skills

Related Topics

Paper Publishing

Paper Publishing