A Low-Power Timing-Error-Tolerant Circuit by Controlling a Clock

Also Available Domains Transistor Logic|Cadence EDA

Objective

The main aim of this project is to implement the timing error tolerant circuit using time borrow scheme for reducing the setup timing violations generated in the next stage

Abstract

This paper presents clock controlling technique in flip flops to prevent timing errors. Timing errors are detected and corrected by modify the clock of flip flop without changing the system clock with minimum logics. Timing error is now getting increased attention due to the high rate of error-occurrence on semiconductors. Even slight external disturbance can threaten the timing margin between successive clocks since the latest semiconductor operates with high frequency and small supply voltage. To deal with a timing error, many techniques have been introduced.

Nevertheless, existing methods that mitigate a timing error mostly have time-delaying mechanisms and too complex operation, resulting in a timing problem on clock-based systems and hardware overhead. In this article, we propose a novel timing-error-tolerant method that can correct a timing error instantly through a simple mechanism. By modifying a clock in a flip-flop, the proposed system can recover a timing error without the loss of time in the clock-based system.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

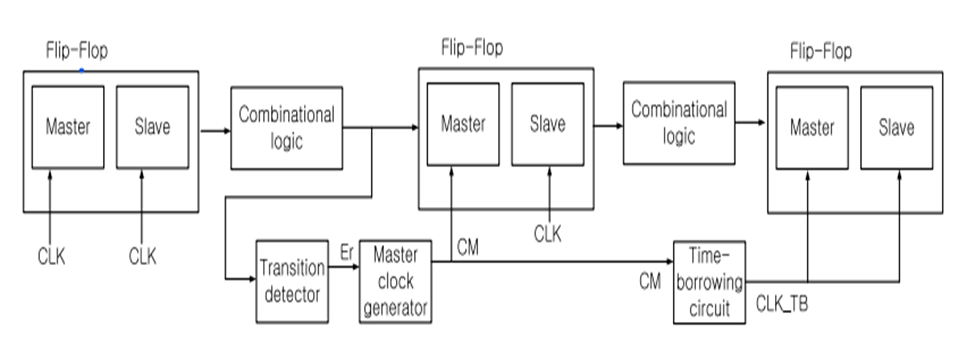

Block Diagram

Specifications

Software Requirements:

- Tanner EDA

- Technology files: 45nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM 3

- 100 MB of available disk space

Learning Outcomes

- Introduction to Timing error tolerant circuits

- Knowledge on error detection techniques

- Knowledge on error detection and correction techniques

- Knowledge on Time borrowing technique.

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for Timing error tolerant circuit

- How to design low power, timing error tolerant circuit by controlling a clock?

- Introduction to Analog Electronics

- Importance of Time borrowing technique

- Scope of Error detection & correction techniques in today’s world

- Applications in Real time.

Paper Publishing

Paper Publishing