A Low-Power High-Speed Sense-Amplifier-Based Flip-Flop in 55 nm MTCMOS

Also Available Domains Cadence EDA|Tanner EDA|Cadence EDA

Objective

The main objective of this work is to reduce the power and to increase the speed of the sense amplifier and the latch was designed with a glitch-free and contention-free. Thus proposed SAFF is a good choice for replacing master-slave flip-flop in digital systems

Abstract

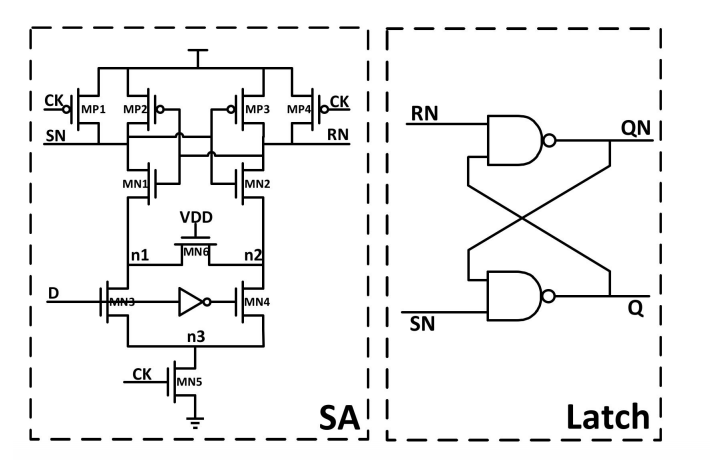

A Sense Amplifier based Flip Flop (SAFF) is suitable for low-power high-speed operation. With the employment of a new sense-amplifier stage as well as a new single-ended latch stage, the power and delay of the flip-flop is greatly reduced. The proposed SAFF can provide low voltage operation by adopting MTCMOS optimization.

The proposed SAFF delay and the power are smaller than those of the existing Master Slave Flip Flop (MSFF). The power-delay-product of the proposed SAFF improves compared with the conventional SAFF and MSFF, respectively the area of the proposed flip-flop decrease, the proposed SAFF could provide robust operation even low power supply voltages. But in this design we are using 45nm technology by using this technology we can get the required output by giving 1 LVT.

Keywords: Low-power, high-speed, Flip Flop, Sense Amplifier, MTCMOS.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Tanner EDA/ Cadence Virtuoso

- Technology files:45nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Introduction to Flipflops

- Importance of sense amplifier based flipflops

- Transistors & its applications

- Types of Transistors

- Logic Gates using Transistors

- Pull Up and Pull Down networks

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for sense amplifier based flipflops

- How to design low power, high speed area efficient transistor level circuits?

- Importance of static power in Lower technology nodes

- Static power reduction techniques

- Scope of sense amplifier-based Flip flops in today’s world

- Applications in real time

- Tanner EDA / Cadence EDA tool for design and simulation

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing