A High-Speed Floating-Point Multiply-Accumulator Based on FPGAs

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

The main objective of this project is to design a floating point multiply accumulator which comprises of signed soft multiplier and a single floating point accumulator.

Abstract

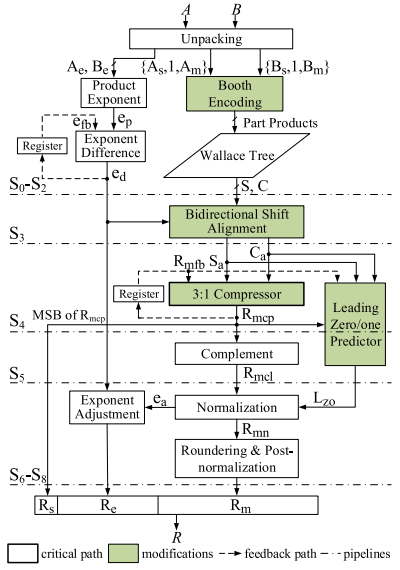

In this article, a novel high-speed floating-point multiply-accumulator (FPMAC) is proposed. It comprises a signed soft multiplier and a single-cycle floating-point accumulator (FAAC). The multiplier is realized by a radix-4 Booth encoding based on sign-magnitude inputs. The FAAC contains a bidirectional shift alignment, a fast 3:1 compressor, and a three-operand leading-zero predictor (LZP). Due to the simplification of implementation steps, a short critical path, and a full-pipelined structure, our FPMAC achieves a high running speed while sustaining the good performance of delay and resource consumption.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Specifications:

Software Requirements:

· Xilinx ISE14.7 Suite/Vivado2018.3 Tool.

· HDL: Verilog.

Hardware Requirements:

· Microsoft® Windows XP.

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support.

· 512 MB RAM.

· 100 MB of available disk space.

Learning Outcomes

Learning Outcomes:

- Basics of Digital Electronics.

- Concept of floating point representation.

- Difference between floating and fixed point representation.

- Introduction to Verilog Coding.

- Different modeling styles in Verilog.

o Data Flow modeling.

o Structural modeling.

o Behavioral modeling.

o Mixed level modeling.

- Introduction to floating point accumulator design.

- About arithmetic operations on floating point numbers.

- Knowledge on single and double floating point precision unit’s representation.

- About approximation computing.

- Applications in real time.

- Xilinx ISE 14.7 Suite/Vivado2018.3 for design and simulation.

- Generation of Netlist.

- Solution providing for real time problems.

- Project Development Skills:

- Problem Analysis Skills.

- Problem Solving Skills.

- Logical Skills.

- Designing Skills.

- Testing Skills.

- Debugging Skills.

- Presentation Skills.

- Thesis Writing Skills.

Paper Publishing

Paper Publishing