A High-Performance Core Micro-Architecture Based on RISC-V ISA for Low Power Applications

Also Available Domains DSP Core|Cadence EDA|Xilinx ISE

Objective

The main objective of this paper is to enhance the operation speed with the help of instruction set architecture. The multiplier and dividers are employed to perform both signed and unsigned operations with less area cost

Abstract

In this project a high performance micro architecture based on RISC-V ISA has been proposed. Design of high-performance processors with very low power requirement is the primary goal of many contemporary and futuristic applications. In this brief, a novel processor micro-architecture is designed which is capable of achieving these requirements. This micro architecture is based on RISC-V Instruction Set Architecture (ISA). The proposed RISC V proposed here is a four stage pipeline architecture with very basic components to get the best possible result. This design consumes a dynamic power which is better than ARM Cortex-M3 and Cortex-M4 and also lower than many others designs. The results show that this core can outperform many existing commercial and open-source cores. The effectiveness of the proposed method is synthesized and simulated using Xilinx Vivado.

Keywords: - Micro-architecture, RV32IM, RISC-V, functional unit, Baugh Wooley, Booth, vedic, Dadda, FPGA, ARM.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

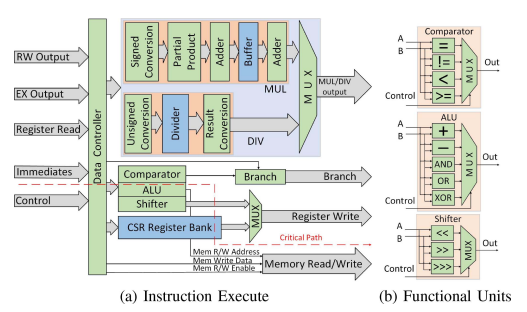

Block Diagram

Specifications

Software Requirements:

Xilinx Vivado Tool

HDL: Verilog

Hardware Requirements:

Microsoft® Windows XP

Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

512 MB RAM

100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to Arithmetic circuits

- Knowledge on multiplier and divider circuits

- Different control units and instructions

- Knowledge on RISC processor

- Applications in real time

- Xilinx Vivado for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing