A High-Efficiency Fast-Transient LDO with Low-Impedance Transient-Current Enhanced Buffer

Also Available Domains Tanner EDA

Objective

The main objective of this paper is to implement Low Dropout Regulator by employing novel buffer. The buffer designed is of low-impedance transient-current enhanced buffer.

Abstract

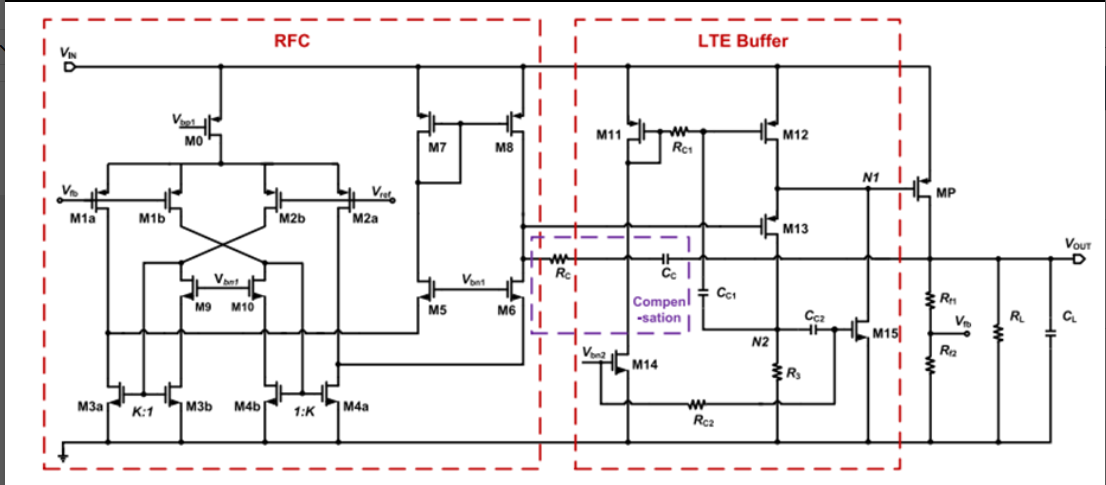

In this paper a low drop out regulator circuit proposed. It uses a fully analog architecture to reduce the power. The proposed architecture is compatible with analog CMOS technology and is capable of operating with a low supply voltage of 1.1 V. In this architecture, A low-dropout regulator (LDO), low-impedance transient-current enhanced (LTE) buffer, recycling-folded-cascode (RFC) are used to design a 1V low drop out regulator circuit The circuit is implemented in Cadence employing gpdk45nm CMOS technology.

Keywords: low-dropout regulator (LDO), low-impedance transient-current enhanced (LTE) buffer, recycling-folded-cascode (RFC)

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Tool: Cadence Virtuoso

- Technology: GPDK 45nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

· Introduction to Analog Electronics

· Basic knowledge on Amplifier

o Different configurations of Amplifier

o Advantages & Applications

· Learning of LTE Buffer

· Knowledge on LDO Concept

· Tool learning in Cadence Virtuoso

· Transistor Level design of LDO in Cadence.

· Analysis of circuit and simulation results.

· Scope of LDO in today’s world

· Real time applications of LDO.

Paper Publishing

Paper Publishing