VLSI Implementation of Turbo Coder for LTE using Verilog HDL

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

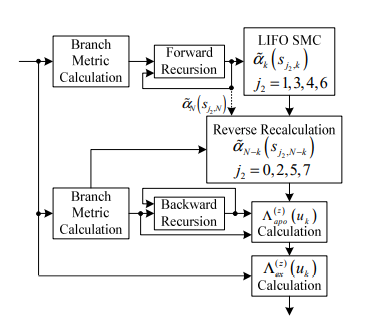

This paper proposes a Very Large Scale Integration (VLSI) architecture for the implementation of Turbo decoder. Soft-in-soft out decoders, interleavers and deinterleavers is used in the decoder side which employs Maximum-a-Posteriori (MAP) algorithm.

Abstract

Turbo codes are error correction codes that are widely used in communication systems. Turbo codes exhibits high error correction capability as compared with other error correction codes. This paper proposes a Very Large Scale Integration (VLSI) architecture for the implementation of Turbo decoder. Soft-in-soft out decoders, interleaves' and deinterleaves is used in the decoder side which employs Maximum-a-Posteriori (MAP) algorithm. The number of iterations required to decode the information bits being transmitted is reduced by the use of MAP algorithm. For the encoder part, this paper uses a system which contains two Recursive convolutional encoders along with pseudorandom inter leaver in encoder side. The Turbo encoding and decoding is done using Octave, Xilinx Vivado, Cadence tools. The system is implemented and synthesized in Application Specific Integrated Circuit (ASIC).Timing analysis has been done and GDSII file has been generated.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

· Tool: Xilinx ISE 14.7 /Xilinx Vivado2018.3

· HDL: Verilog

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Introduction to turbo encoder and decoder

- Knowledge on TURBO architecture

- Different instruction sets

- Knowledge on encoder and decoder

- Applications in real time

- Xilinx ISE 14.7/Xilinx Vivado2018.3 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing