Vlsi Implementation of Reversible Fir Filter Design

Also Available Domains Arithmetic Core

Project Code :TVMATO665

Objective

The main aim of this project is to design a novel Filter which is used in DSP applications. In this project, FIR filter was designed by using Ripple Carry Adder and multiplier.

Abstract

In this paper, we proposed a high FIR filter

design using reversible logic gates. we

are proposing different multiplier design by realizing the partial products of

the multiplier circuit using reversible gates known as reversible partial

product generator thereby developing a reversible Wallace multiplier design. We

have used PG gate and Feynman' block as reversible half-adder (HA) and

full-adder (FA) in the adder network, respectively. By using this reversible

logic gates, we are implemented the Ripple carry adder and Wallace tree

multiplier design. The complexity, simulated outputs and the speed parameters

for the adder circuit have been discussed.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

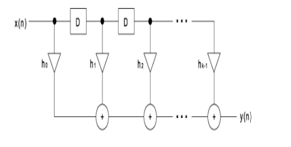

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to reversible logic

- About reversible gates

- Knowledge on FIR filter

- Knowledge on architectural designs of feynman, peres gates etc

- Applications in real time

- Xilinx ISE 14.7/Xilinx Vivado for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Demo Video

Related Topics

Paper Publishing

Paper Publishing