VLSI Design of Pipelined FFT Architecture for DSP Application

Objective

The main objective of this paper is to implement single delay feedback FFT.

Abstract

The rapid advancements in digital signal processing (DSP) applications have led to an increased demand for efficient and high-performance architectures to implement complex algorithms such as the Fast Fourier Transform (FFT). In this study, we present a VLSI design of a pipelined FFT architecture specifically tailored for DSP applications. The proposed architecture aims to address the challenges associated with real-time processing, power consumption, and resource utilization. It leverages the inherent parallelism in the FFT algorithm and utilizes a pipelining technique to achieve high throughput and reduce latency. Additionally, careful consideration is given to minimize area overhead and power consumption. The architecture is implemented using Very Large Scale Integration (VLSI) techniques, allowing for integration into dedicated DSP processors or system-on-chip (SoC) designs. The design is optimized for area efficiency, making it suitable for resource-constrained applications while still achieving high performance. To validate the effectiveness of the proposed design, extensive simulations and comparisons are performed against existing FFT architectures. The results demonstrate the superiority of the pipelined FFT architecture in terms of throughput, latency, and power efficiency.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

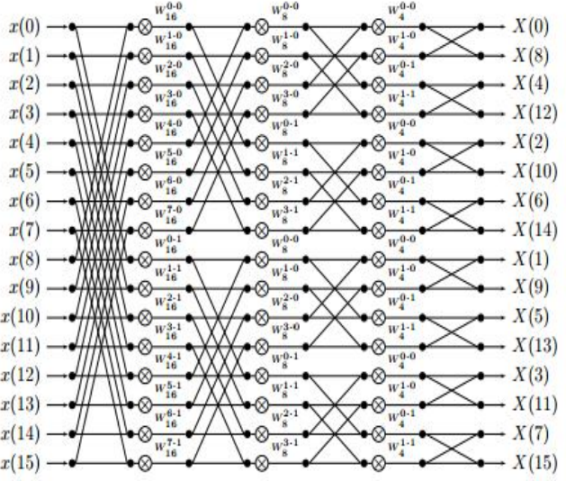

Block Diagram

Specifications

Software Requirements:

· Xilinx ISE14.7 Suite/Vivado2018.3 Tool.

· HDL: Verilog.

Hardware Requirements:

· Microsoft® Windows XP.

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support.

· 512 MB RAM.

· 100 MB of available disk space.

Learning Outcomes

• Basics of Digital Electronics

• FPGA design Flow

• Introduction to Verilog Coding

• Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

• Drawbacks of existing methods

• Applications in real time

• Xilinx ISE 14.7/Xilinx Vivado for design and simulation

• Generation of Netlist

• Solution providing for real time problems

• Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Debugging Skills

Paper Publishing

Paper Publishing