VLSI Architecture for High Performance Wallace Tree Encoder

Also Available Domains Cadence EDA|Low Power VLSI|Tanner EDA

Abstract

ABSTRACT

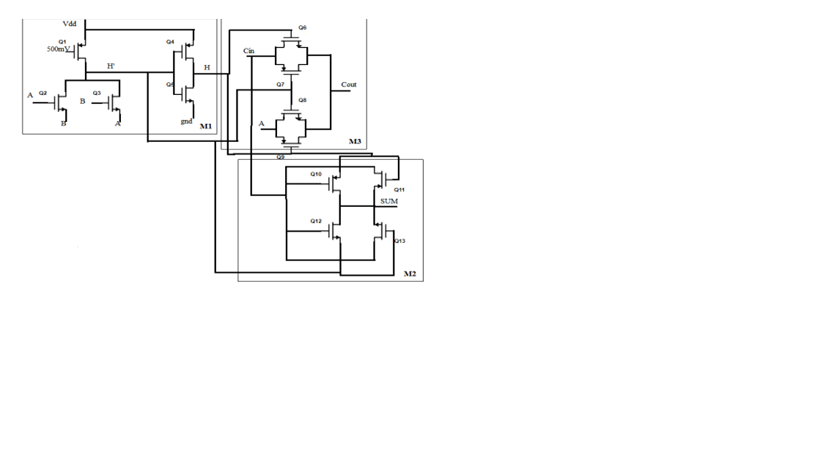

In the research, the VLSI architecture design for Wallace tree encoder with modified full adder is proposed. In analog to digital conversion process, Wallace tree encoder is utilized in the process of converting the thermometer code to binary. This can be termed to be a high speed application and a flash type of flash ADC, which is a resistor ladder, encoder and comparator circuit. A suitable encoder is required for getting binary code from comparator output. Reducing energy of the encoder is a vital concern whereas designing the minimal power flash form ADC. Wallace tree encoders diminishes the mistake due to the availability of zeroes in the sequence of the once presence to the series of zeroes in a comparator output, but it consumes more power. Hence in the proposed work, a low power Wallace tree encoder is designed using pass transistor logic (PTL) full adder. The design is implemented using Cadence Virtuoso tool employing gpdk 45nm technology.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

· Tool: Tanner EDA/Cadence Virtuoso/LT spice

· Technology: 45nm.

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

· Understanding Clocking Techniques

· Power Optimization Techniques

· Advantages and Applications

· Low-Power Design Principles.

· Timing Analysis and Performance Optimization

· Tool Learning in Tanner EDA/Cadence Virtuoso

· Analysis of design and simulation results

· Noise Immunity and Signal Integrity

Paper Publishing

Paper Publishing