Reseeding LFSR for Test Pattern Generation

Objective

Proposed model reduces the need for memory to store seed value and the power utilization.

Abstract

Testing of circuits became difficult as the scale of integration is increasing as said in Moore’s Law. Conventional testing approach is not sufficient with the growth of device counts and density. Testing helps the developer to investigate faults and error present in developed circuit which helps to reduce time require to test and thus decreases chances of getting failed during operation. Test time is one of the most important parameters in digital circuit testing which effects the overall process of testing. Reducing the test time of the test pattern generation is one of the most effected solution for the process. Reseeding LFSR is one of the methods to generate the test patterns for testing. In this paper, pseudo-random test patterns are generated to test circuit using reseeding LFSR technique. This helps to reduce the test pattern required to be stored for testing. This technique can be applied with the principles which are required for low power as well as low test data volume. Proposed model reduces the need for memory to store seed value and the power utilization. Reseeding can mainly be applied for BIST which targets complete fault coverage and minimization of the test length. Data compression for reducing the test pattern required for testing will indirectly reduce the time required to check the circuits. Future work is to reduce time required for the test pattern generation. Hamming distance can be applied to calculate the number of bits changing during the test patterns transition. Hamming distance approach can be implemented to reduce the parameter.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

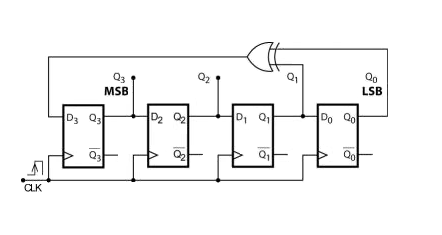

Block Diagram

Paper Publishing

Paper Publishing