RandShift: An Energy-Efficient Fault-Tolerant Method in Secure Nonvolatile Main Memory

Also Available Domains Communications and Crypto Core|Xilinx Vivado

Objective

The main objective of this paper is to reduce the error rate and power in encrypted data encoded by the Advanced Encryption Standard. This paper is implemented with the randomness feature of AES encryption as well as rotational shift operation to tolerate hard faults in nonvolatile memory cells

Abstract

In this paper, we present a simple, yet energy-

and area-efficient method for tolerating the stuck-at faults caused by an endurance

issue in secure-resistive main memories. In the proposed method, by employing

the random characteristics of the encrypted data encoded by the Advanced

Encryption Standard (AES) as well as a rotational shift operation, a large number

of memory locations with stuck-at faults could be employed for correctly

storing the data. The proposed RandShift technique, which is simple and energy

efficient due to its one-time recomputation of the AES encryption for each data

written to the PCM main memory. Due to the simple hardware implementation of the

proposed method, its energy consumption is considerably smaller than that of

other recently proposed methods. The fault coverage of the proposed method is

similar to that of the existing method. In this article, we present a simple

energy-efficient method to tolerate the stuck-at faults in the PCM main memory

when encrypted data are stored on it.

Keywords: Advanced Encryption Standard (AES), Error Correction Code, Rand Shifter, nonvolatile memories

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

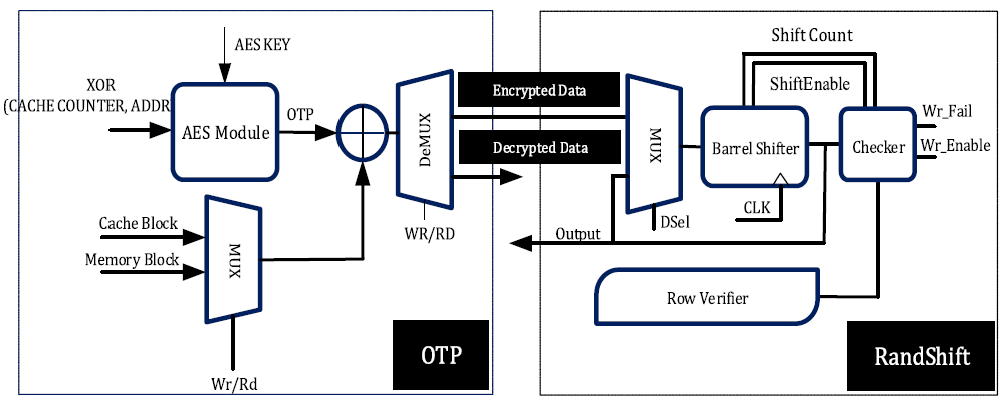

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Combinational & Sequential circuits

- About Non-volatile memories

- Testing concepts

- Stuck-at-zero & stuck-at-one faults

- Knowledge on Advance Encryption Standard

- Randshift Method

- Error Correction Code

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing