Performance Evaluation of Fixed-point Array Multipliers on Xilinx FPGAs

Objective

This work considers the implementation of two widely used fixed-point bit-parallel multipliers on Xilinx Spartan-6 FPGAs.

Abstract

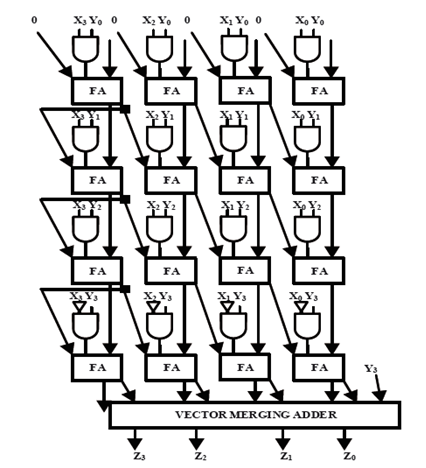

Multiplication is one of the frequently used arithmetic operation in digital signal processing. It forms the core element in many complex operations like Filtering, Fast Fourier Transforms, Convolution etc. Since these circuits perform key operations in signal processing, their speed and power optimization are crucial quality factors. Evidently, fixed-point representation has gained a lot of importance when hardware realization of multipliers is considered. Traditionally, three implementation styles have been used viz. bit-parallel, bit-serial and digit-serial. However, bit-parallel systems are preferred in performance-critical applications because of their ability to process multiple bits in parallel. This work considers the implementation of two widely used fixed-point bit-parallel multipliers on Xilinx Spartan-6 FPGAs. These include parallel Ripple Carry Array multipliers and parallel Carry Save Array multipliers. A distinguishing feature of this work is that the realizations are carried out using LUT instantiations. This is in contrast to previous realizations, where inferential codes are used to represent the functionality of the design and the synthesizer decides the mapping of the coded functionality, thereby, resulting in sub-optimal realizations. We have compared our realizations against some conventional multiplier designs. Experimental analysis using Xilinx Spartan-6 FPGA reveals that our approach results in a substantial improvement in performance with a little runtime overhead.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing