Performance Analysis of Wallace Tree Multiplier with Kogge Stone Adder using 15-4 Compressor

Objective

In this paper, a design approach of 16bit Wallace Tree approximate multiplier with 15-4 compressor is considered to provide more reliability.

Abstract

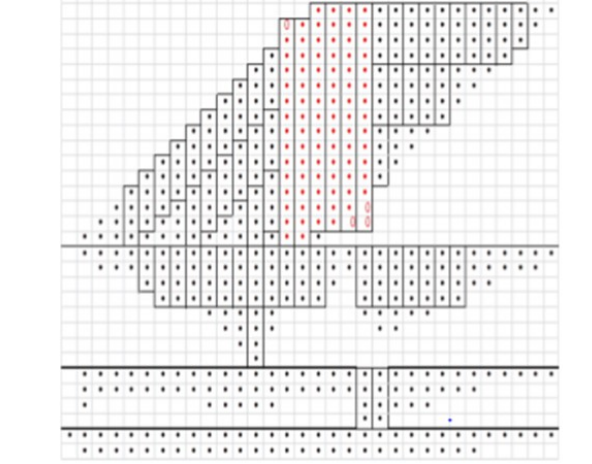

The major role of electronics device is to provide low power dissipation and compact area with high speed performance. Among the major modules in digital building blocks system, multiplier is the most complex one and main source of power dissipation. Approximate Computing to multiplier design plays major role in electronic applications, like multimedia by providing fastest result even though it possesses low reliability. In this paper, a design approach of 16bit Wallace Tree approximate multiplier with 15-4 compressor is considered to provide more reliability. The 16×16 Wallace tree multiplier is synthesized and simulated using Xilinx ISE 14.5 software. The multiplier occupies about 15% of total coverage area. The dissipated power and delay of the multiplier are 0.042μw, 3.125ns respectively.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing