One-Sided Schmitt-Trigger-Based 9T SRAM Cell for NearThreshold Operation

Also Available Domains Core Memories|Tanner EDA|Cadence EDA

Abstract

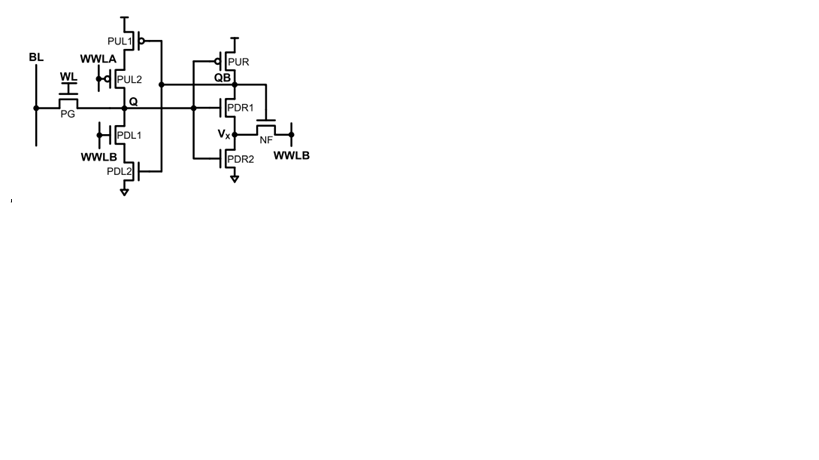

Abstract: This paper presents a one-sided Schmitt-trigger based 9T static random access memory cell with low energy consumption and high read stability, write ability, and hold stability yields in a bit-interleaving structure without write-back scheme. The proposed Schmitt-trigger-based 9T static random access memory cell obtains a high read stability yield by using a one-sided Schmitt-trigger inverter with a single bit-line structure. In addition, the write ability yield is improved by applying selective power gating and a Schmitt-trigger inverter write assist technique that controls the trip voltage of the Schmitt-trigger inverter.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

· Tanner EDA/Cadence Tool

· Technology files: 45nm

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Introduction to SRAM

- Different Configurations of SRAM

- Working of SRAM

- Knowledge on Near Threshold region

- Knowledge on Sub-threshold region

- Limitations & Applications.

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for 9T SRAM

- How to design SRAM using ST inverters

- Introduction to Analog Electronics

- Importance of Schmitt trigger

- Scope of SRAM in today’s world

Paper Publishing

Paper Publishing