Novel Ternary Adder and Multiplier Designs Without Using Decoders or Encoders

Also Available Domains Transistor Logic

Objective

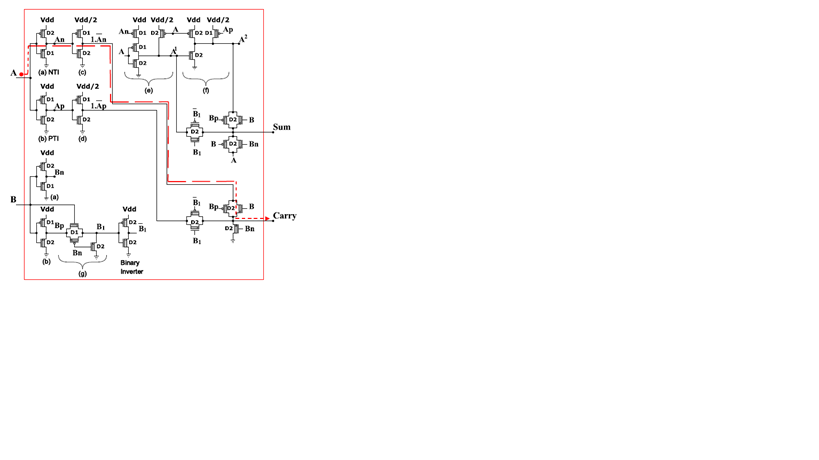

In this project, the 32 nm CNTFET-based Ternary Half Adder (THA) and Multiplier (TMUL) circuits use novel ternary unary operator circuits and implement two power supplies Vdd and Vdd/2 without using any ternary decoders, basic logic gates, or encoders to minimize the number of used transistors and improve the energy efficiency.

Abstract

Abstract:

In this project, the 32 nm CNTFET-based Ternary Half Adder (THA) and Multiplier (TMUL) circuits use novel ternary unary operator circuits and implement two power supplies Vdd and Vdd/2 without using any ternary decoders, basic logic gates, or encoders to minimize the number of used transistors and improve the energy efficiency. Multiple-Valued Logic systems present significant improvements in terms of energy consumption over binary logic systems. This paper proposes new ternary combinational digital circuits that reduce energy consumption in low-power nano-scale embedded systems and Internet of Thing (IoT) devices to save their battery consumption.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

· H-spice

· Technology files: 32nm

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Introduction to Ternary circuits, adders, multipliers

- Need of designing adders and multipliers using ternary logic

- Transistors & its applications

o Types of Transistors

o Logic Gates using Transistors

o Pull Up and Pull Down networks

o Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for ternary multipliers and adders.

- How to design low power, high speed area efficient transistor level circuits?

- Drawbacks in CMOS technology

- Scope of ternary logic in today’s world

- Applications in real time

- H-Spice tool for design and simulation

- Solution providing for real time problems

Paper Publishing

Paper Publishing