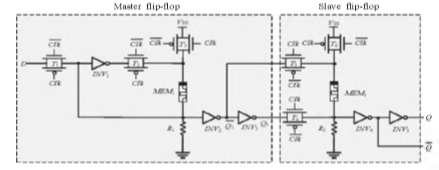

Novel Memristor-based Nonvolatile D Latch and Flip-flop Designs

Abstract

Sequential devices are the fundamental building blocks for almost all digital electronic systems with memory. Due to the importance of instant data recovery after unexpected data loss such as unplanned power down, sequential devices need to have the nonvolatile property, which motivates the recent research and practice in integrating the nonvolatile memristors into CMOS devices. In this paper, we study how to apply this approach to improve the quality of nonvolatile D latch. Unlike the structure of conventional design, the proposed D latch consists of only one memristors, several transmission gates, and CMOS inverters. Our design overcomes the negative effect due to the threshold loss of the transistors. As simulation shows, compared with the current designs, our proposed memristors based D latch can support the memristors to switch between different resistance states much faster, and thus achieving a clock of higher frequency. In addition, our design allows the threshold value of the memristors to be selected from a much wider range.

Keywords:D latch,memristors,master-slave D flip-flop, nonvolatile

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- H-spice

- Technology files: 45nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Introduction to Memristor, Flipflops

- Need of Memristor based Flipflops

- Transistors & its applications

- Types of Transistors

- Logic Gates using Transistors

- Pull Up and Pull Down networks

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Memristor level design of Flipflops.

- How to design low power, high speed area efficient transistor level circuits?

- Drawbacks in CMOS technology

- Scope of Memristor based d Flipflops in today’s world

- Applications in real time

- H-Spice tool for design and simulation

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing