New VLSI BWA Architecture for Finding the First W Maximum/minimum Values using Sorting Algorithm

Also Available Domains Communications|Xilinx Vivado

Abstract

Low density parity check (LDPC) codes have been extensively

adopted in next-generation

forward error correction applications because they achieve very good

performance using the iterative decoding approach of the belief-propagation

(BP). The basic decoder design for achieving the highest decoding throughput is

to allocate processors corresponding to all check and variable nodes, together with

an interconnection network. In this fully-parallel

decoder architecture, the hardware complexity due to the routing overhead is

very large. Therefore, much of the work on LDPC decoder design has been

directed towards achieving optimal tradeoffs between hardware complexity and

decoding throughput. In particular, a

time-multiplexed or folded approach, which is known as partially parallel

decoder architecture, has been proposed. Low hardware layered decoding

architecture for LDPC code scheme is proposed using only one switch network

with direct connections. This method requires only one shuffle network, rather

than the two shuffle networks which are used in conventional designs. In

addition, this project can be extended to block parallel decoding scheme by

suitably mapping

between required memory banks and processing units in order to increase the

decoding throughput.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

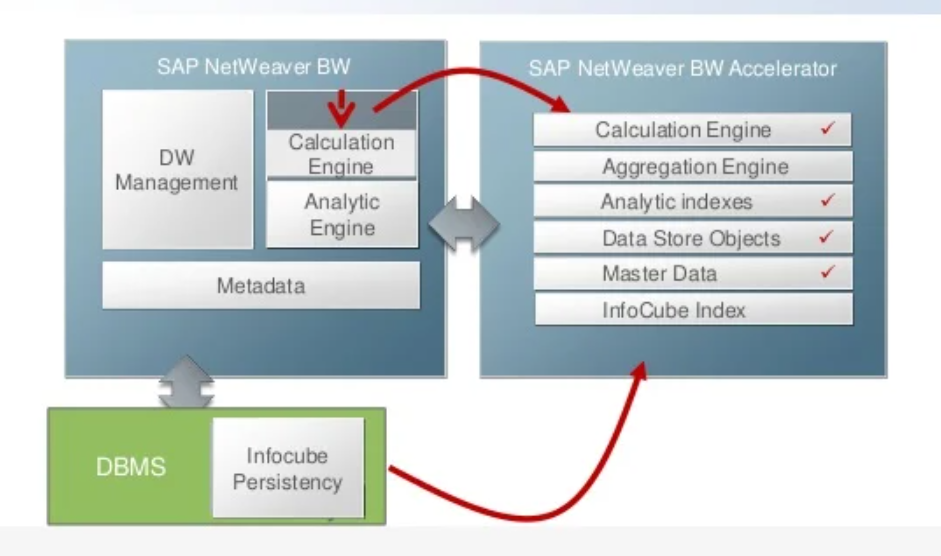

Block Diagram

Specifications

System Configuration:-

In the hardware part a normal computer where Xilinx ISE 14.3 software can be easily operated is required, i.e., with a minimum system configuration

Hardware requirement

Processor - Pentium –III

Speed - 1.1 GHz

RAM - 1 GB (min)

Hard Disk - 40 GB

Floppy Drive - 1.44 MB

Key Board - Standard Windows Keyboard

Mouse - Two or Three Button Mouse

Monitor - SVGA

Software requirements

v Operating System :Windows95/98/2000/XP/Windows7

v Front End : Modelsim 6.3 for Debugging and Xilinx 14.3 for Synthesis and Hard Ware Implementation

v This software’s where Verilog source code can be used for design implementation.

Learning Outcomes

Understanding of sorting algorithms: Students will gain in-depth knowledge of various sorting algorithms, including their operation, complexity analysis, and suitability for hardware implementation. They will learn about sorting algorithms such as quicksort, mergesort, heapsort, or other efficient algorithms suitable for VLSI architectures.

Knowledge of VLSI design principles: Students will learn the principles and techniques of VLSI design, including digital circuit design, hardware description languages (HDLs), and the implementation of algorithms in hardware. They will understand the trade-offs between performance, area, and power consumption in VLSI designs.

Familiarity with hardware implementation techniques: Students will become familiar with the hardware implementation techniques required to build the VLSI architecture, including datapath and control unit design, memory management, and interconnect design. They will gain practical experience in designing and optimizing hardware circuits for efficient sorting.

Designing efficient architectures: Students will learn how to design VLSI architectures that efficiently solve specific problems, such as finding the first W maximum/minimum values. They will understand how to leverage sorting algorithms to achieve this objective and optimize the architecture for speed, area, and power consumption.

Performance analysis: Students will analyze the performance of the VLSI architecture in terms of throughput, latency, and resource utilization. They will learn how to evaluate the efficiency of the sorting algorithm implementation and the overall architecture, considering the desired number of maximum/minimum values (W) and the size of the input data.

Troubleshooting and debugging: Students will develop skills in troubleshooting and debugging hardware designs, identifying and resolving issues that may arise during the VLSI implementation process. They will gain experience in identifying and mitigating potential bottlenecks and optimizing the architecture for improved performance.

Documentation and presentation skills: Students will enhance their skills in documenting their VLSI design process, including writing clear and concise design specifications, test plans, and implementation reports. They will also develop presentation skills to effectively communicate their work and findings to a technical audience.

Collaboration and teamwork: If the project is conducted in a group or collaborative setting, students will learn to work together effectively, distribute tasks, and integrate individual contributions into a cohesive VLSI architecture. They will gain experience in coordinating and collaborating with team members to achieve project objectives.

Paper Publishing

Paper Publishing