Machine Learning Based Power Efficient Approximate 4:2 Compressors for Imprecise Multipliers

Objective

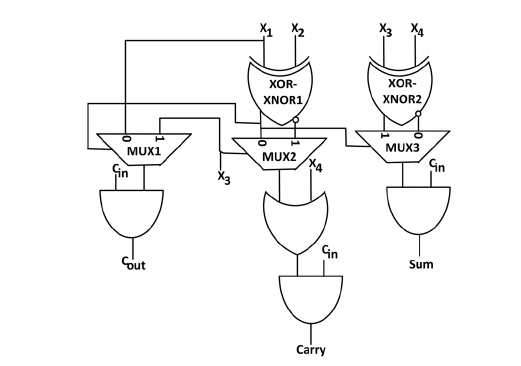

This paper presents a 4:2 compressors with inexact logic minimization by flipping some of the output bits considering efficiency / accuracy into account.

Abstract

Machine Learning (ML) has been one of the applications of approximate circuits. These circuits, part of approximate computing, can be implemented using either probabilistic pruning or inexact logic minimization. Since low power consumption

and smaller silicon area are the critical parameters in portable devices, approximate circuits have been the current topic for discussion. This paper presents a 4:2 compressors with inexact logic minimization by flipping some of the output bits considering efficiency/accuracy into account. The proposed 4:2 compressor has been utilized in an 8 × 8 Dadda multiplier and average power, area and propagation delay of the architectures have been computed. All the simulations have been performed using spectre simulator of Cadence Design Systems in 45nm technology node. To find the difference between the exact and approximate proposed circuits, error analysis has been performed using

MATLAB. The application idea of this paper is to employ Python TensorFlow in Google Co Laboratory© to Upload, download the approximate 4:2 compressor which has been implemented in Cadence Virtuoso.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Paper Publishing

Paper Publishing