Low Power 4-Bit Arithmetic Logic Unit using Full-swing GDI Technique

Objective

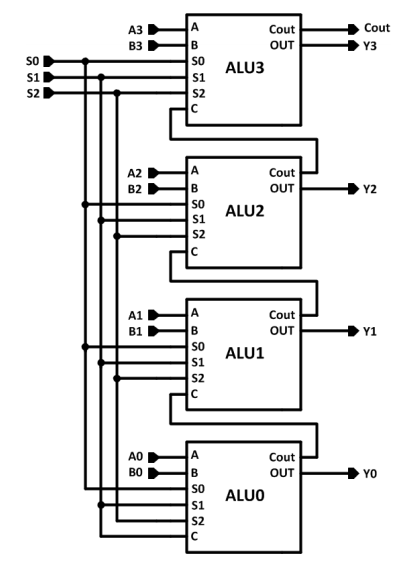

The main objective of this project is to design the 4-bit ALU in order to achieve low power consumption having full swing output voltage using GDI Technique.

Abstract

Power dissipation and area of the circuit are the main issues in the electronics industry, this paper provides a design of 4-Bit Arithmetic Logic Unit (ALU) using Full-Swing GDI Technique, which considered an effective method for low power digital design while reducing the area of the circuit compared to other logic styles. The proposed ALU design consists of 2×1 Multiplexer, 4×1 Multiplexer and low power Full Adder cell to realize the arithmetic and logic operations. The simulation carried out using Cadence Virtuoso using 65nm TSMC process. The results show that the proposed design consume less power using less number of transistors, while achieving full swing operation compared to previous work.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing