Low Power 1-Bit Full Adder using Full-Swing Gate Diffusion Input Technique

Objective

This paper presents a design which provides full swing output for logic 1 and logic 0 for 1-bit full adder cell and reduces power consumption, delay, and area.

Abstract

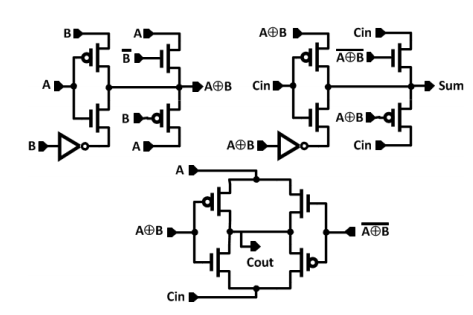

This paper presents a design which provides full swing output for logic 1 and logic 0 for 1-bit full adder cell and reduces power consumption, delay, and area. In this design full adder consists of two XOR gate cells and one cell of 2×1 multiplexer (MUX). The performance of the proposed design compared with the different logic style for full adders through cadence virtuoso simulation based on TSMC 65nm technology models with a supply voltage of 1v and frequency 125MHz. The simulation results showed that the proposed full adder design dissipates low power, while improving delay and area among all the design taken for comparison.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing