Implementation of Delayed LMS algorithm based Adaptive filter using Verilog HDL

Objective

This paper focuses on the implementation of Delayed Least Mean Square algorithm based Adaptive filter in Verilog HDL.

Abstract

Abstract:

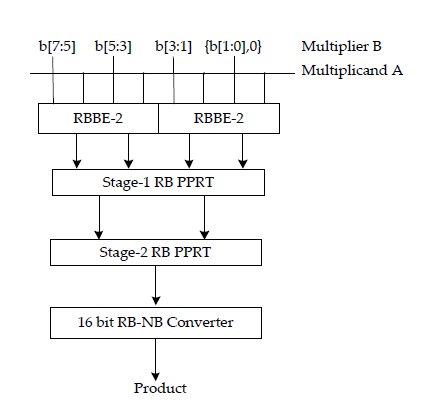

In this work, the development of an adaptive filter based on the Delayed Least Mean Square algorithm in Verilog HDL is the main topic. A better, more effective structure for the LMS algorithm, termed the Delayed LMS algorithm (D-LMS), is suggested. The Least Mean Square (LMS) method is based on an adaptive filter, and its structure is briefly reviewed. Block carry look ahead adder and multiplier are described as essential building elements for the creation of the D-LMS Adaptive filter. To demonstrate how much faster the D-LMS method converges, the implemented D-LMS adaptive filter is synthesized and compared to an adaptive filter based on the LMS algorithm.

Keywords: LMS Algorithm, Adaptive filter, Critical path, Verilog HDL, FPGA synthesis.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Specifications:

Software Requirements:

· Xilinx Vivado

Minimum Hardware Requirements:

· Microsoft® Windows 7

· Intel® i3 processor or equivalent with SSE support

· 4GB RAM

· 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Filters

- Writing code in Verilog.

- Introduction to Least Mean Square.

- Knowledge on combinational and sequential circuits.

- Applications in real time

· Xilinx Vivado for design, synthesis and simulation

· Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing