Image Enhancement using Edge Spartan 6 FPGA Board

Also Available Domains FPGA

Objective

The main objective of this work is to enhance the contrast of the gray image by using hardware software co-simulation for image processing in Xilinx System Generator.

Abstract

Image Processing is used to modify pictures to improve their quality and extract structured information. Image enhancement methods are used to increase the photographic quality of images. Enhancement can be performed to gray image with size 128 * 128. The main objective of any enhancement method is obtaining a more suitable result compared with the original form. To implement image processing algorithms using high level languages requires thousands of lines of code which is inefficient as it takes more time. Alternate solution is using Xilinx System Generator, which is a modeling tool where design is captured by using Xilinx block set from library environment. This project presents concept of hardware software co-simulation for image processing using Xilinx System Generator (XSG). This technique provides a set of Simulink blocks (models) for several hardware operations that could be implemented on various Xilinx FPGA.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

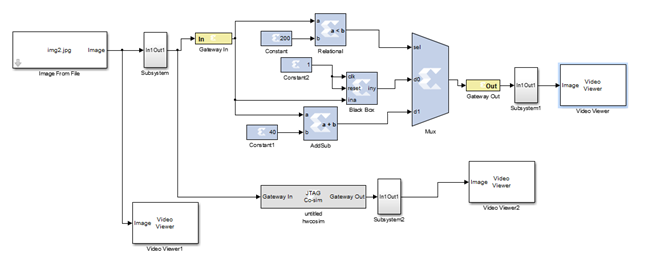

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7& MATLAB 2013b

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP,

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Combinational & Sequential circuits

- Knowledge on Arithmetic circuits

- About Simulink block

- About Xilinx System generator

- Knowledge on piece wise linear transformation

- Applications of multipliers in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing