High-Precision and Low-Power Offset Canceling Tri-State Sensing Latch in NAND Flash Memory

Objective

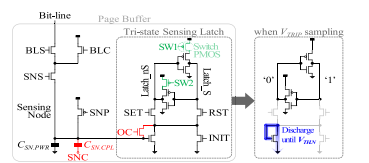

In this brief, the offset canceling tri-state sensing latch (OCTSL) is proposed that achieves high-precision and low-power read operation.

Abstract

This paper presents a novel approach to enhance the precision and reduce power consumption in NAND flash memory read operations through the introduction of a High-Precision and Low-Power Offset Canceling Tri-State Sensing Latch (HPLP-OCTSL). The proposed HPLP-OCTSL architecture leverages tri-state sensing to enable high-resolution read operations, allowing for finer distinctions between programmed memory states. By incorporating offset cancelation techniques, the architecture mitigates the influence of various sources of offset errors, such as device mismatches and temperature variations. This results in a significant improvement in the reliability and precision of read operations in NAND flash memory. Through simulations and empirical testing, we demonstrate that the proposed design achieves remarkable improvements in precision and power efficiency, making it a promising candidate for next-generation NAND flash memory systems.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

· Tool: Tanner EDA

· Technology: 45nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

· Introduction to digital & analog electronics

· Knowledge of MOSFETs

o Operation and characteristics of PMOS & NMOS

o Knowledge on Threshold voltages

· Basics of Latch

o Operation of Latch & its applications

· Importance of offset parameter in analog electronics

· Knowledge on CMOS Configuration

· Knowledge on Tool Learning

· Scope of Sense Amplifiers in Real time.

Paper Publishing

Paper Publishing