Fully Automated Traffic Light Controller system for a four-way intersection using Verilog

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

The main objective of this project is to design the fully automated traffic light controller using clock divider for timing control and FSM for reducing power consumption.

Abstract

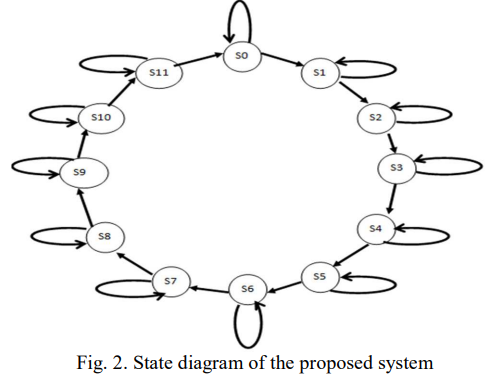

Traffic lights are placed in roads to control the flow of traffic and to prevent accidents. This paper proposes a Moore machine based fully automated and efficient traffic light controller system for four-way intersection. The system is designed on Xilinx Artix-7 xc7a100tcsg324-1 FPGA using Xilinx ISE14.7/Xilinx Vivado2018.3 and Verilog Hardware Description Language. The designed system runs up to a maximum operating frequency of 10 MHz’s.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

· Xilinx ISE14.7 suite/ Xilinx Vivado2018.3.

· HDL: Verilog.

Hardware Requirements:

o Microsoft® Windows XP.

o Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support.

o 512 MB RAM.

o 100 MB of available disk space.

Learning Outcomes

· Basics of Digital Electronics.

· Concept of FSM.

· Concept of FPGA’s.

· Concept of light emitting diode.

· Introduction to Verilog Coding.

· Different modelling styles in Verilog.

· Data Flow modelling.

· Structural modelling.

· Behavioural modelling.

· Mixed level modelling.

· Introduction to traffic signal controller system.

· Knowledge on FSM.

· About approximation computing.

· Applications in real time.

· Concept on design and simulation tool

· Generation of Netlist.

· Solution providing for real time problems.

· Project Development Skills:

o Problem Analysis Skills.

o Problem Solving Skills.

o Logical Skills.

o Designing Skills.

o Testing Skills.

o Debugging Skills.

o Presentation Skills.

o Thesis Writing Skills.

Paper Publishing

Paper Publishing