Fast Mapping and Updating Algorithms for a Binary CAM on FPGA

Also Available Domains Communications and Crypto Core|Xilinx Vivado

Objective

The main objective of this paper is to speed up the table makeup and reduce the energy consumption for the mapping and updating algorithms for a binary CAM on FPGA algorithm selects at most one layer of SRAM blocks for contents updating at any location rather than activating the entire memory blocks and ultimately consumes less energy during the update process.

Abstract

Farming is a process which involves various steps. These steps are done manually by the farmers. With the advent of technology various researches are done in this field. Usually, the process is extremely tedious when carried out manually. This paper concerns with an FPGA design-based implementation of a low-cost advanced sowing machine controller that was built as a project of a VLSI design using Verilog HDL. The implemented sowing machine controller serves many purposes and is one of the real and complex controller systems to revolutionize agriculture industry. It is well equipped with some advanced sensors. Speed and area optimization have been the areas of concern while designing the system.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

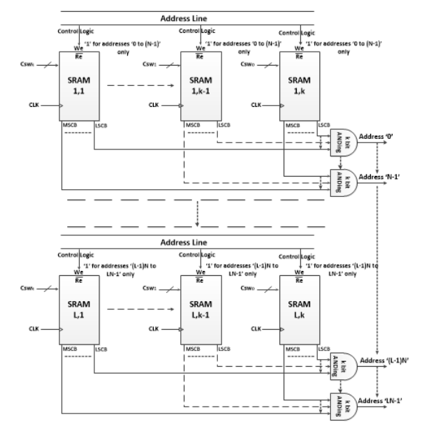

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7 Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Concept of Content Addressable Memory

- Importance of addressable memories

- Drawbacks of existing methodologies

- Introduction to CAM

- Knowledge on BiCAM

- Knowledge on various types of addressable memories

- Applications of CAM in real time

- Scope of TCAM concept in today’s world

- Applications in real time

- Xilinx ISE 14.7/Xilinx Vivado for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing