Factorized Carry Look Ahead Adder

Objective

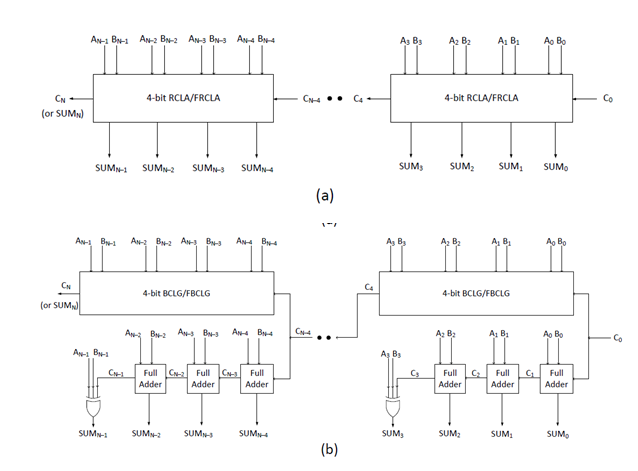

The idea behind the proposed factorized carry look ahead adders is discussed and example implementations are provided.

Abstract

New factorized carry look ahead adders corresponding to the regular carry look ahead adder (RCLA) architecture viz. the factorized regular carry look ahead adder (FRCLA), and the block carry look ahead adder (BCLA) architecture viz. the factorized block carry look ahead adder (FBCLA) are presented. The idea behind the proposed factorized carry look ahead adders is discussed and example implementations are provided. The RCLA, BCLA, FRCLA and FBCLA were realized using the gates of a 32/28nm CMOS standard digital cell library. The results show that the proposed FRCLA achieves an average reduction in the power-delay product i.e., energy by 7.85% for 32- and 64-bit additions compared to the best among the rest.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing