Energy-Quality Scalable Design Space Exploration of Approximate FFT Hardware Architectures

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

This paper presents a comprehensive design space exploration for boosting energy efficiency of a fast Fourier transform (FFT) VLSI accelerator, exploiting several approximate multipliers (Ax M) combined with approximate adder (Ax A) circuits.

Abstract

This paper presents a comprehensive design space exploration for boosting energy efficiency of a fast Fourier transform (FFT) VLSI accelerator, exploiting several approximate multipliers (Ax M) combined with approximate adder (Ax A) circuits. The FFT hardware herein presented consists of a fixed-point sequential architecture using a radix-2 butterfly with decimation in time. We explore a set of Ax Ms – namely Dynamic Range Unbiased (DRUM), Rounding-based Approximate (Ro BA), leading one Bit-based Approximate (Lo BA), and Truncated approach – jointly with the LOA, ETA-I, Copy A, Copy B, Trunc0, Trunc1 approximate adders. The approximate arithmetic operators are used in the butterfly kernel with exploration of the approximation levels (for the L and K least-significant bits, respectively, for the Ax M and Ax A), aiming at discovering the most energy-efficient configuration under a design-time QoR constraint. The mean square error and peak signal-to-noise ratio metrics define which approximate levels combining L and K variations will enable the FFT to process signals to generate spectrograms without significant losses. Our results show that the Lo BA multiplier with L=8 together with the LOA, Trunc1 and Trunc0, at different approximation levels, provide most energy savings with controllable quality degradation, presenting a minimum decrease of 20.2% in power dissipation without degrading the spectrogram generation quality.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

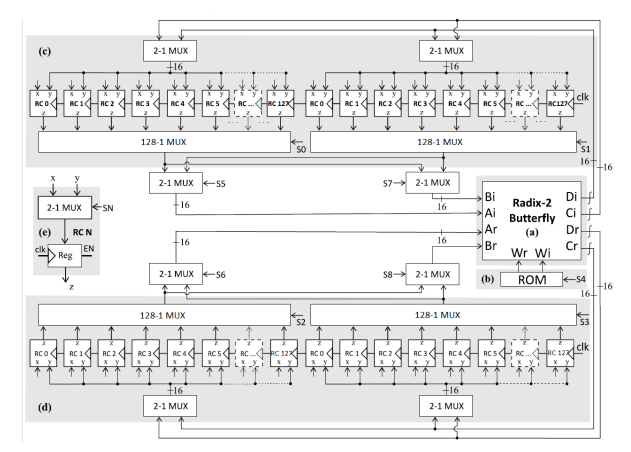

Block Diagram

Specifications

Software Requirements:

· Tool: Xilinx ISE 14.7/ XilinxVivado2018.3

· HDL: Verilog

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Introduction to Fourier Transform

- Knowledge on Discrete Fourier Transform and Fast Fourier Transform

- Different multipliers such as complex multiplier and constant multipliers

- Knowledge on energy quality scalable

- Applications in real time

- Xilinx ISE 14.7/Xilinx Vivado2018.3 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing