Energy-Efficient Approximate Multiplier Design using Bit Significance-Driven Logic Compression

Objective

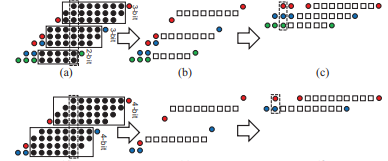

In this paper, we propose a novel energy-efficient approximate multiplier design using a significance-driven logic compression (SDLC) approach.

Abstract

Approximate arithmetic has recently emerged as a promising paradigm for many imprecision-tolerant applications. It can offer substantial reductions in circuit complexity, delay and energy consumption by relaxing accuracy requirements. In this paper, we propose a novel energy-efficient approximate multiplier design using a significance-driven logic compression (SDLC) approach. Fundamental to this approach is an algorithmic and configurable lossy compression of the partial product rows based on their progressive bit significance. This is followed by the commutative remapping of the resulting product terms to reduce the number of product rows. As such, the complexity of the multiplier in terms of logic cell counts and lengths of critical paths is drastically reduced. A number of multipliers with different bit-widths (4-bit to 32-bit) are designed in Verilog and synthesized using Xilinx ISE Design suite.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing