Efficient Implementations of 4-Bit Burst Error Correction for Memories

Objective

In this brief, efficient solutions to protect memories against 4-bit bursts are presented.

Abstract

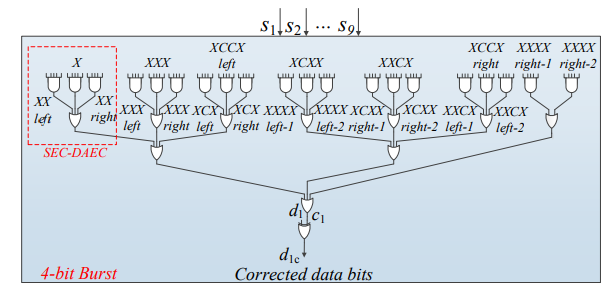

In recent years, there has been a growing interest in error correction codes (ECCs) that can correct localized errors in memories. This is due to the larger fraction of radiation induced error events that affect several nearby memory cells as technology scales. Initially, codes that can correct single and double adjacent errors were proposed. More recently, 3-bit burst ECCs have also been presented. The next step is to provide efficient 4-bit burst error correction for memories. The issue is that as the error correction capability increases so does the overheads required to implement the codes in terms of parity check bits and encoding and decoding complexity. In this brief, efficient solutions to protect memories against 4-bit bursts are presented. The first one is the use of two interleaved single and double adjacent ECC while in the second, efficient 4-bit burst ECCs are presented. The first solution reduces the decoding complexity and delay at the cost of having more parity check bits while the second tries to reduce the decoding complexity when using the minimum number of parity check bits. Both solutions have been evaluated and compared to an interleaved single error correction code and with existing burst ECCs to better understand the overheads needed to achieve the protection against 4-bit burst errors.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing