Effective Hardware Accelerator for 2D DCT IDCT Using Improved Loeffler Architecture

Also Available Domains DSP Core|Xilinx Vivado

Objective

In this implementation, a DCT/IDCT hardware architecture using loeffler algorithm with multiplier les DCT was proposed. To implement multiplier less DCT, CDS encoding was implemented and thereby the efficiency of the design of DCT has been optimized.

Abstract

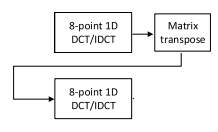

Using an enhanced Loeffler architecture, this study suggests a powerful hardware accelerator for the 2D 8 8 discrete cosine transform (DCT) and inverse discrete cosine transform (IDCT). The Loeffler 8-point 1D DCT/IDCT data stream is optimised by the accelerator based on the needs of image and video processing. By equitably dividing the amount of clock cycles and streamlining the arithmetic operations in each cycle, an 8-stage pipeline layout significantly increases processing speed. Using both fixed-point and canonic signed digit (CSD) coding, adders and shifters are used to create the multiplication-free approximation of the DCT coefficients. In particular, the row-column coefficient conversion function is accomplished with less circuit complexity using the fast parallel transposed matrix architecture that is suggested.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Specifications:

Software Requirements:

· Xilinx ISE 14.7 Tool

· HDL: Verilog

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

Learning Outcomes:

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Introduction to multiplier design

- About conventional multiplication process

- Knowledge on partial product generation and reduction

- Knowledge on adders, compressors

- About CSD encoding

- Knowledge on constant multipliers using CSD encoding

- Applications in real time

· Xilinx ISE 14.7 for design and simulation

· Generation of Netlist

· Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing