Design and Performance Analysis of Various 32-bit Hybrid Adders using Verilog

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

The main objective of this paper is to implementation of different type of 32-bit VLSI adders will be done using differing types of combination of adders and logic.

Abstract

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

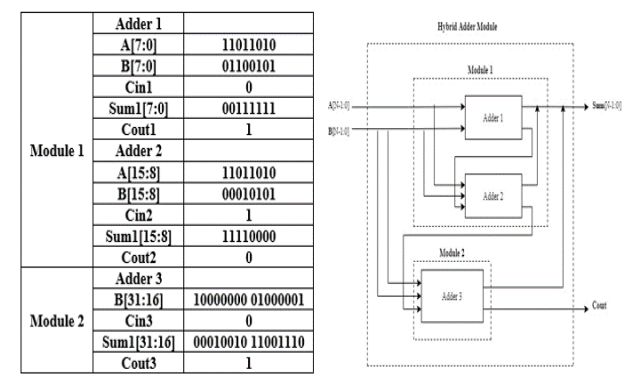

Block Diagram

Specifications

Software Requirements:

· Xilinx ISE14.7 suite/Xilinx Vivado2018.3.

· HDL: Verilog.

Hardware Requirements:

o Microsoft® Windows XP.

o Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support.

o 512 MB RAM.

o 100 MB of available disk space.

Learning Outcomes

· Basics of Digital Electronics.

· Concept of binary addition.

· Different types of binary adders.

· Introduction to Verilog Coding.

· Different modeling styles in Verilog.

· Data Flow modeling.

· Structural modeling.

· Behavioral modeling.

· Mixed level modeling.

· Introduction to adders design.

· About hybrid addition process.

· Knowledge on propagation of sum and carry.

· Knowledge on adders.

· About approximation computing.

· Applications in real time.

· Xilinx ISE14.7 suite / Xilinx Vivado2018.3 for design and simulation.

· Generation of Netlist.

· Solution providing for real time problems.

· Project Development Skills:

o Problem Analysis Skills.

o Problem Solving Skills.

o Logical Skills.

o Designing Skills.

o Testing Skills.

o Debugging Skills.

o Presentation Skills.

o Thesis Writing Skills.

Paper Publishing

Paper Publishing