Design and Analysis of FPGA Based 32 Bit ALU Using Reversible Gates

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

The main aim of this project is to implement the ALU design using reversible gates. By using the reversible gates like fredkin and Peres, the power will be reduced

Abstract

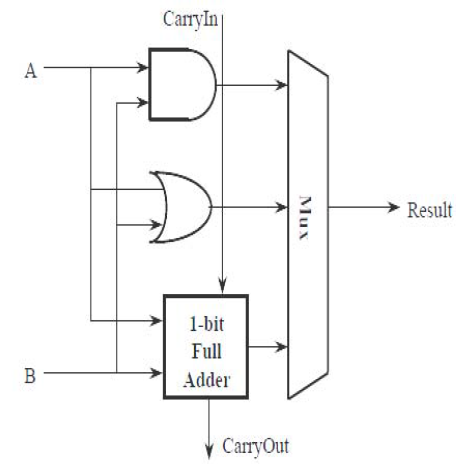

In this project, we are implementing a reversible ALU circuits in which convention irreversible gates are replaced using reversible logic gates. Here we are proposing reversible ALU circuit for addition operation. An Arithmetic logic Unit (ALU) is used in arithmetic, logical function in all processor. It is also an important subsystem in digital system design. Arithmetic Logic Unit (ALU) is one of the most important components of any system and is used in many appliances like calculators, cell phones, and computers .A 32-bit ALU was designed using reversible logical gates such as Peres gate, fredkin gate etc,. Which replaces the AND and OR for each one bit ALU circuit. The design here implemented can work fast than the ALU existing processor using less power. The design of an ALU and a Cache memory for use in a high performance processor was examined. Reversible logic vital in recent years because it has ability to reduce the power dissipation which is main requirement in low power design. This technique helps in reducing power consumption and power dissipation. This paper presents an implementation of ALU based on reversible logic while comparing it to an ALU architecture with the normal logic gates in terms of power consumption and delay leading to the improvement of performance of ALU circuit. The effectiveness of the proposed method is synthesized and simulated using Xilinx ISE 14.7.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to Arithmetic circuits

- About reversible logic

- Knowledge on ALU circuits

- Different reversible gates

- Knowledge on adder designs using reversible gates

- About quantum computing

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing