Design of MAC Unit in Artificial Neural Network Architecture using Verilog HDL

Also Available Domains Arithmetic Core|Xilinx Vivado

Objective

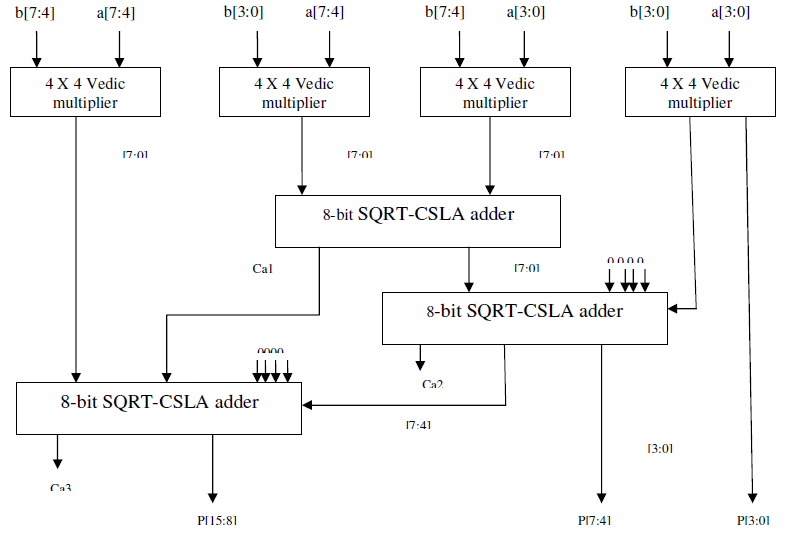

The main aim of this work is to implement the MAC unit which is used in Neural Network applications. The MAC architecture was designed by using vedic multiplier with reduced delay architecture

Abstract

In this project we are implementing MAC unit which is used in an Artificial neural network (ANN) is parallel Information processing structure consists of processing units. The processing unit decides while the network is efficient or not. So need to design an efficient processing unit and it also provide better performance. The processing unit consists of MAC unit (Multiplication and Accumulation) and Activation unit. In an existing system, the processing MAC unit was designed by Booth multiplier and carry look ahead adder. The existing processing unit provides delay and consumes more area and power. To overcome the drawbacks, designed a new processing unit, Vedic multiplier with square root carry select adder (SQRT-CSLA). The proposed design overcomes the drawbacks of the existing system, and it’s also providing better performance of the entire network. The Activation function unit was designed by sigmoid neurons process. Entire processing unit was implemented and verified by using Verilog HDL language. The effectiveness of the proposed method is synthesized and simulated using Xilinx ISE 14.7.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Introduction to Artificial Neural Networks

- About logic gates

- Knowledge on BEC

- Different adders

- Knowledge on adder designs using logic gates

- About SQRT-CSL adder

- Vedic multiplication

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing