Design of Low Power Magnitude Comparator

Project Code :TVMI20

Objective

The proposed magnitude comparator using the technology of coupling has been compared with the basic comparator circuit.

Abstract

A low power two bit magnitude comparator has been proposed in the present work. The proposed magnitude comparator using the technology of coupling has been compared with the basic comparator circuit. The performance analysis of both the different comparators has been done for power consumption, delay and power delay-product (PDP) with VDD sweep. The simulations are carried on Mentor graphics (T-Spice) using 90nm CMOS technology at 1 V supply.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

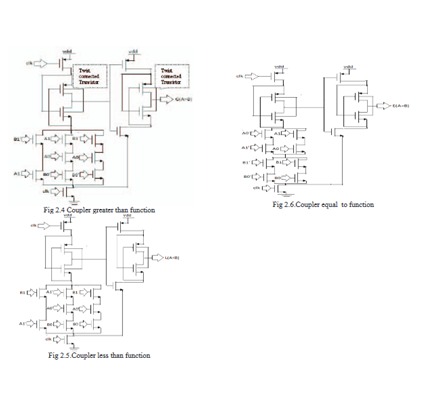

Block Diagram

Specifications

24/7 Support,,

Video On Demand,

Remote Connectivity,

Code Customization,

Customization,

Live Chat Support,

Toll Free Support

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing