Design and Verification of 16 bit RISC Processor Using Vedic Mathematics

Also Available Domains DSP Core|Xilinx ISE

Project Code :TVPGTO596

Objective

The main aim of this paper is that the multiplier unit in Arithmetic and Logic Unit (ALU) and Multiplier and Accumulator (MAC) is implemented using Vedic Sutras reduce computation delay and improve the performance of the RISC design.

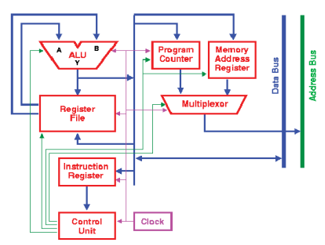

Block Diagram

Specifications

Software Requirements:

- Xilinx Vivado Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to Arithmetic circuits

- Knowledge on MAC unit

- Different control units and instructions

- Knowledge on RISC processor

- Applications in real time

- Xilinx Vivado for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Demo Video

Related Topics

Paper Publishing

Paper Publishing