Design and Synthesis of a 256-Point Radix-2 DIT FFT Core with Design Ware Library using Fixed-Point Number Representation

Also Available Domains Xilinx Vivado|Arithmetic Core

Objective

The main objective of this paper is to implementation of a 256-point DIT (Decimation in Time) FFT algorithm with fixed-point number representation.

Abstract

In digital image processing, a time-domain image is converted to the frequency domain to carry out operations such as image enhancing or noise reduction. Discrete time domain image is converted to the frequency domain using Discrete Fourier Transform (DFT) and this lies at the heart of any image processing algorithm. Apart from image processing, Fourier Transform is used in a wide variety of applications from simple radio broadcasting to complication object recognition for autonomous driving purposes. To reduce the computation time of DFT, Fast Fourier Transform (FFT) algorithm was proposed by James W. Cooley and John W. Tukey in 1965. This involved breaking down the DFT of N-length sequence into smaller DFTs of N/2-length with even and odd index terms. DFT can further be broken into real and imaginary parts and accurate representation of this is done through fixed-point number representation in hardware. A fixed-point number consists of a decimal part and a fraction part and arithmetic operations around this type of number representation often require pipelined logic structure to increase throughput. So, in this paper, the implementation of a 256-point DIT (Decimation in Time) FFT algorithm with fixed-point number representation in Verilog is discussed. The synthesis and simulation of the proposed designs can be implemented using Xilinx ISE14.7.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

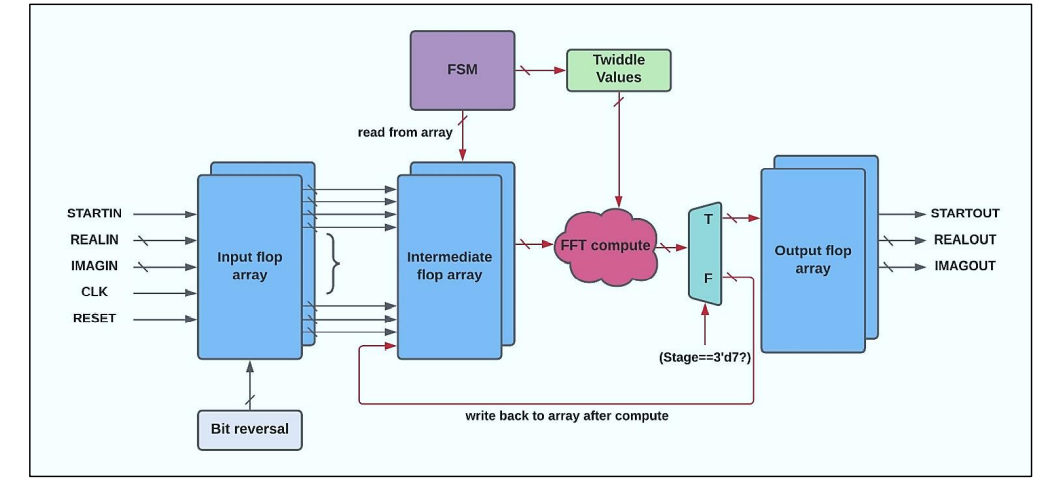

Block Diagram

Specifications

Software Requirements:

· Xilinx ISE14.7 Suite.

· HDL: Verilog.

Hardware Requirements:

· Microsoft® Windows XP.

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support.

· 512 MB RAM.

· 100 MB of available disk space.

Learning Outcomes

- Basics of Digital Electronics.

- Concept of FFT.

- Difference between FFT and IFFT.

- Introduction to Verilog Coding.

- Different modeling styles in Verilog.

o Data Flow modeling.

o Structural modeling.

o Behavioral modeling.

o Mixed level modeling.

- Introduction to signals and systems.

- About DIT FFT.

- Knowledge on Radix-2 FFT algorithm.

- Knowledge fixed point representation.

- About approximation computing.

- Applications in real time.

- Xilinx ISE14.7 Suite for design and simulation.

- Generation of Netlist.

- Solution providing for real time problems.

- Project Development Skills:

o Problem Analysis Skills.

o Problem Solving Skills.

o Logical Skills.

o Designing Skills.

o Testing Skills.

o Debugging Skills.

o Presentation Skills.

o Thesis Writing Skills.

Paper Publishing

Paper Publishing