Design and Simulation of CRC Encoder and Decoder using VerilogHDL

Objective

In this paper, an efficient CRC (8) encoder and decoder circuits have been designed and implemented using Verilog HDL.

Abstract

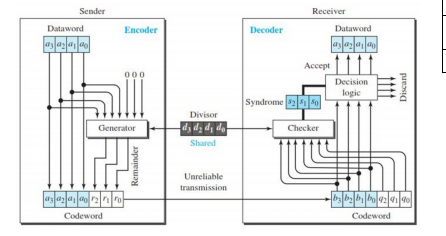

Cyclic Redundancy Check (CRC) technique is an efficient error detection method which used to detect single and burst errors. CRC technique adds redundancy bits to the original dat. The redundancy bits represent the remainder of division between the original message and the selected polynomial. At the receiver side, the received data can be recognized as valid or not. In this paper, an efficient CRC (8) encoder and decoder circuits have been designed and implemented using Verilog HDL. Xilinx ISE 14.7 Simulator is used for circuits verification and validation for CRC (8) (Cyclic Redundancy Checking with an input 8-bit polynomial), 5 and 8-bit input data. The results reveal that the proposed circuits are efficient in terms of hardware utilization rate.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing