Design and implementation of subway automatic ticketing system based on Verilog HDL

Also Available Domains Finite State Machines

Objective

The main objective of this project is to implement automatic ticketing system using FSM to reduce power consumption

Abstract

This paper is a synthesis of practical investigation, theoretical analysis and literature reading. Using Verilog HDL language to research a subway automatic ticket selling system. The design of this subway ticketing system takes convenience, quickness and simplicity as the core, and takes saving time for passengers as the guide design. It completes the main process of buying subway tickets for passengers. Firstly, this paper studies the development of subway ticketing system at home and abroad, and then studies the basic components of subway ticketing system. The paper also simulates the ticket selection module, coin calculation module, and change processing module and display interface module on Xilinx vivado2018.3/Xilinx ISE14.7 suite.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

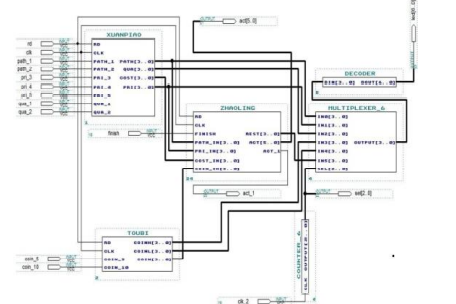

Block Diagram

Specifications

Software Requirements:

· Xilinx ISE 14.7 suite / Xilinx Vivado 2018.3 Tool.

· HDL: Verilog.

Hardware Requirements:

· Microsoft® Windows XP.

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support.

· 512 MB RAM.

· 100 MB of available disk space.

Learning Outcomes

- Basics of Digital Electronics.

- Concept on FSM.

- Introduction to Verilog Coding.

- Different modeling styles in Verilog.

o Data Flow modeling.

o Structural modeling.

o Behavioral modeling.

o Mixed level modeling.

- Introduction to subway ticketing system

- About approximation computing.

- Applications in real time.

· Concept on design and simulation tool.

· Generation of Netlist.

· Solution providing for real time problems.

· Project Development Skills:

o Problem Analysis Skills.

o Problem Solving Skills.

o Logical Skills.

o Designing Skills.

o Testing Skills.

o Debugging Skills.

o Presentation Skills.

o Thesis Writing Skills.

Paper Publishing

Paper Publishing