Design and Implementation of Arbitrary Point FFT Based on RISC-V SoC

Also Available Domains DSP Core|Xilinx Vivado

Project Code :TVPGTO631

Objective

Designs and implements a dedicated microprocessor architecture based on the RISC-V (the fifth-generation Reduced Instruction Set Computing) with only 20 instructions for arbitrary-point FFT (Fast Fourier Transform) algorithm

Abstract

In this project, a dedicated microprocessor

architecture based on the RISC-V (the fifth generation Reduced Instruction Set

Computing) with only 20 instructions for arbitrary-point FFT (Fast Fourier

Transform) algorithm has been proposed. Moreover, the corresponding SoC (System-on-Chip)

is also built for the expansibility and re-configurability. The methodology of

software and hardware co-verification is applied to validate the correctness of

the systematic functions by comparing the simulation results between MATLAB,

Visual Studio 2019 and VIVADO 2019.1. Finally, the Xilinx Artix-7

(XC7A100TFGG484- 2) FPGA (Field Programmable Gate Array) platform is used for

implementation and prototyping of the proposed hardware system, which totally

uses 1897 LUTs (Look-Up Tables), 361 FFs (Flip-Flops) and 25 BRAMs (Block

Random Access Memory) and consumes 2.016W at 100MHz. The experimental results

show that the presented system can realize the FFT algorithm at any point by

reconfiguring the parameters of software and expanding the capacity of the

memory, and it is suitable for the embedded applications due to the small area

and low power consumption.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

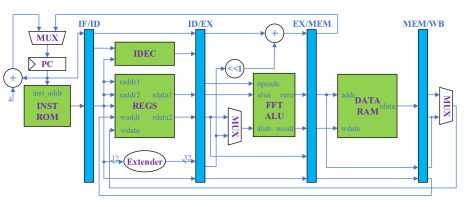

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7 Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to DFT

- Knowledge on RISC V architecture

- Different instruction sets

- Knowledge on FFT

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Related Topics

Paper Publishing

Paper Publishing